#### **CRANFIELD UNIVERSITY**

#### SOHAIB ASLAM

# DESIGN FOR PROGNOSTICS AND SECURITY IN FIELD PROGRAMMABLE GATE ARRAYS (FPGAs)

## SCHOOL OF AEROSPACE, TRANSPORT AND MANUFACTURING

Doctor of Philosophy Academic Year: 2017 - 2020

Supervisor: Prof. Ian K Jennions Associate Supervisor: Dr. Mohammad Samie March 2020

#### CRANFIELD UNIVERSITY

## SCHOOL OF AEROSPACE, TRANSPORT AND MANUFACTURING

**Doctor of Philosophy**

Academic Year 2017 - 2020

#### **SOHAIB ASLAM**

## DESIGN FOR PROGNOSTICS AND SECURITY IN FIELD PROGRAMMABLE GATE ARRAYS (FPGAs)

Supervisor: Prof. Ian K Jennions Associate Supervisor: Dr. Mohammad Samie March 2020

This thesis is submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy

© Cranfield University 2020. All rights reserved. No part of this publication may be reproduced without the written permission of the copyright owner.

#### **ABSTRACT**

There is an evolutionary progression of Field Programmable Gate Arrays (FPGAs) toward more complex and high power density architectures such as Systems-on-Chip (SoC) and Adaptive Compute Acceleration Platforms (ACAP). Primarily, this is attributable to the continual transistor miniaturisation and more innovative and efficient IC manufacturing processes. Concurrently, degradation mechanism of Bias Temperature Instability (BTI) has become more pronounced with respect to its ageing impact. It could weaken the reliability of VLSI devices, FPGAs in particular due to their run-time reconfigurability. At the same time, vulnerability of FPGAs to device-level attacks in the increasing cyber and hardware threat environment is also quadrupling as the susceptible reliability realm opens door for the rogue elements to intervene. Insertion of highly stealthy and malicious circuitry, called hardware Trojans, in FPGAs is one of such malicious interventions. On the one hand where such attacks/interventions adversely affect the security ambit of these devices, they also undermine their reliability substantially. Hitherto, the security and reliability are treated as two separate entities impacting the FPGA health. This has resulted in fragmented solutions that do not reflect the true state of the FPGA operational and functional readiness, thereby making them even more prone to hardware attacks. The recent episodes of Spectre and Meltdown vulnerabilities are some of the key examples. This research addresses these concerns by adopting an integrated approach and investigating the FPGA security and reliability as two inter-dependent entities with an additional dimension of health estimation/ prognostics. The design and implementation of a small footprint frequency and threshold voltage-shift detection sensor, a novel hardware Trojan, and an online transistor dynamic scaling circuitry present a viable FPGA security scheme that helps build a strong microarchitectural level defence against unscrupulous hardware attacks. Augmented Kernel-based learning for efficient technique FPGA health estimation/prognostics, the optimal integrated solution proves to be more dependable and trustworthy than the prevalent disjointed approach.

#### Keywords:

Reliability, Hardware Trojans, Kernel Learning, Negative and Positive Bias Temperature Instability (N/PBTI), Cybersecurity, Threshold Voltage.

**ACKNOWLEDGEMENTS**

I dedicate this valuable piece of intensive research and intellect to my father, who

has always been the prime source of motivation and inspiration for me towards

undertaking this arduous journey of immense worth. His unconditional love and

support throughout my life have kept me sailing smoothly during moments of

distress and disbelief.

Dr. Mohammad Samie, my associate supervisor, has been an influential part of

my academic development, and I owe him my special gratitude for persevering

my sluggishness all these years of research. He has been much more than an

academic advisor to me - a good friend, fantastic human being, and a lively

caring person to share thoughts with. I thank him for his guidance and selfless

help during this time.

Prof. Ian K Jennions, my supervisor, has always been a source of inspiration for

me. His wisdom and supportive nature are second to none. I thank him for his

consistent encouragement.

In particular, I would like to specially thank my viva panel comprising, Dr. Lucian

Prodan, Dr. Hongmei He, and Dr. Ioannis Giannopoulos for examining my

research work in a highly professional manner and rendering extremely useful

guidance on enhancing its impact.

Friendship with Alex, my Ph.D. mate, meant a lot to me, as I could always rely on

him for help and good company. Lastly, the love and encouragement from my

wife and children got me all the strength to carry on; thank you all.

Sohaib, Cranfield, UK, March 2020

ii

### **TABLE OF CONTENTS**

| ABSTRACT                                                             | i            |

|----------------------------------------------------------------------|--------------|

| ACKNOWLEDGEMENTS                                                     | ii           |

| LIST OF FIGURES                                                      | V            |

| LIST OF TABLES                                                       | x            |

| LIST OF EQUATIONS                                                    | xii          |

| LIST OF ABBREVIATIONS                                                | xiv          |

| 1 Introduction                                                       | 15           |

| 1.1 Motivation                                                       | 15           |

| 1.2 Research Aim and Objectives                                      | 17           |

| 1.3 Research Methodology                                             | 18           |

| 1.4 Organisation of Thesis                                           | 20           |

| 1.5 List of Published/Submitted Work                                 | 23           |

| 2 Unified Framework for Health and Security of FPGAs                 | 26           |

| 2.1 Introduction                                                     |              |

| 2.2 Realm of Reliability in FPGAs                                    | 31           |

| 2.3 Realm of Security in FPGAs                                       | 43           |

| 2.4 Integrated FPGA Health Management (IFHM) Framework               | 54           |

| 2.5 Summary                                                          | 58           |

| 3 Understanding the Hardware Trojans in FPGAs                        | 66           |

| 3.1 Introduction                                                     | 66           |

| 3.2 Threat Model and Taxonomy                                        | 67           |

| 3.3 Trojans in FPGA Fabric                                           | 72           |

| 3.4 Trojans in FPGA Tool Chain                                       | 73           |

| 3.5 FPGA Attacks and a Case Study                                    | 75           |

| 3.6 Trojan Countermeasures                                           | 84           |

| 3.7 Summary                                                          |              |

| 4 FREquency Degradation (FRED) Detection and Measurement Sensor      | 91           |

| 4.1 Introduction                                                     |              |

| 4.2 Current Research on Frequency/Delay Variability Detection        | 93           |

| 4.3 FREquency Degradation (FRED) Detection Sensor – Architecture     | 97           |

| 4.4 Implementation Results and Analysis – Simulation and Experiments |              |

| 4.5 Performance Evaluation of FRED                                   | 117          |

| 4.6 Summary                                                          | 122          |

| 5 FPGA Security Scheme                                               |              |

| 5.1 Introduction                                                     | 127          |

| 5.2 Related Work                                                     |              |

| 5.3 FPGA Security Scheme and Threshold Voltage – Triggered Hardware  | <del>)</del> |

| Trojan                                                               |              |

| 5.4 Design and Implementation of a Threshold Voltage-Aware Sensor    | 152          |

| 5.5 Mitigating the Impact of Threshold Voltage – Triggered Hardware  | <u>;</u> |

|----------------------------------------------------------------------|----------|

| Trojan                                                               | 169      |

| 5.6 Implementation and Optimisation of Hardware Trojan Mitigation    | l        |

| Scheme                                                               | 175      |

| 5.7 Summary                                                          | 179      |

| 6 FPGA Health Estimation Using Kernel Learning Approach              | 188      |

| 6.1 Introduction                                                     | 189      |

| 6.2 Kernel Learning and FPGA Health Estimation/Prognostics - A       | 1        |

| Mathematical Interpretation                                          | 191      |

| 6.3 The Developed Kernel Learning Method                             | 194      |

| 6.4 Implementation Results and Analysis – Simulation and Experiments | 199      |

| 6.5 Summary                                                          | 212      |

| 7 Discussion and Conclusions                                         | 216      |

| 7.1 Addressing the Research Aim and Objectives                       | 216      |

| 7.2 Contribution to Knowledge                                        | 219      |

| 7.3 Future Work                                                      | 221      |

| APPENDICES                                                           | 226      |

|                                                                      |          |

### **LIST OF FIGURES**

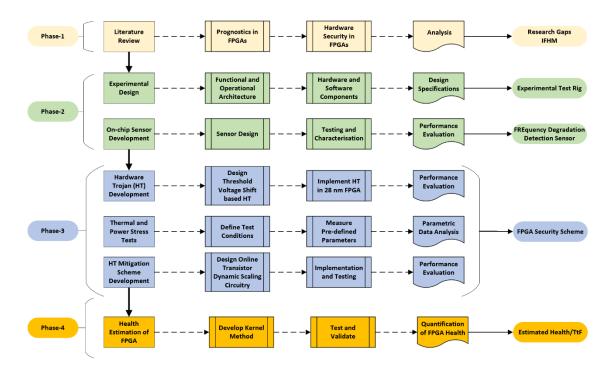

| Figure 1-1  | Research Methodology Process Flow Diagram. 1                                                                                                                                                                                                                                                                          |    |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

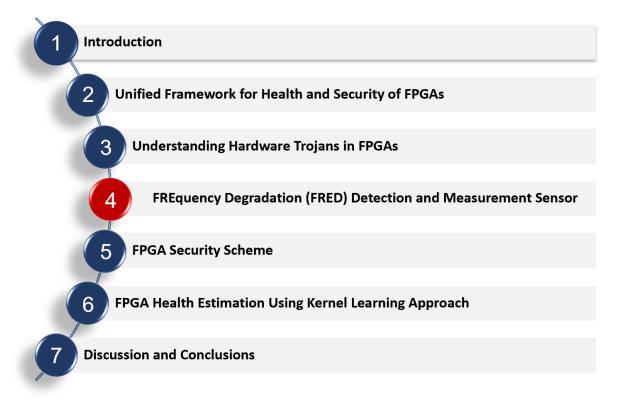

| Figure 1-2  | Thesis Organisation – Disposition of Chapters                                                                                                                                                                                                                                                                         |    |  |

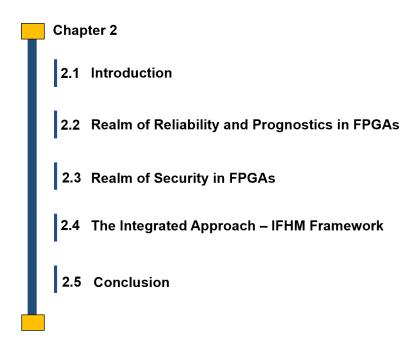

| Figure 2-1  | The Disposition of Chapter 2.                                                                                                                                                                                                                                                                                         |    |  |

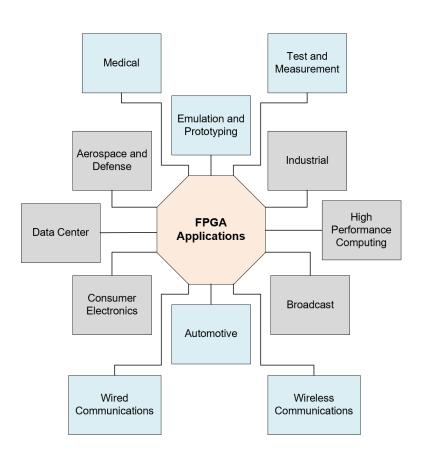

| Figure 2-2  | A Gamut of FPGA Applications.                                                                                                                                                                                                                                                                                         |    |  |

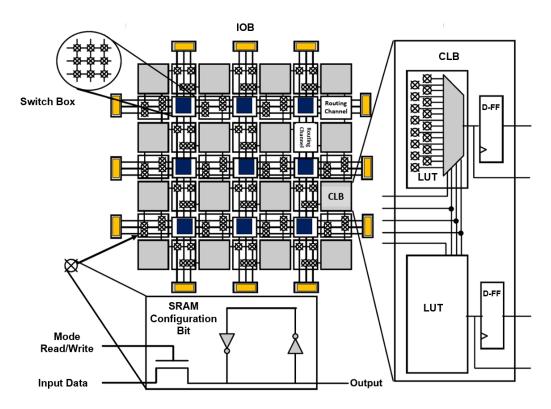

| Figure 2-3  | An architecture of a typical FPGA. The Configuration Logic Blocks (CLBs) are islands with a mesh of programmable interconnects around them. Each CLB houses a Lookup Table (LUT) that can be configured to implement any logic gate.                                                                                  |    |  |

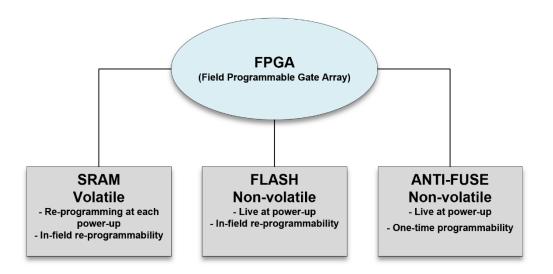

| Figure 2-4  | Three Types of FPGAs – SRAM, FLASH, and ANTI-FUSE.                                                                                                                                                                                                                                                                    |    |  |

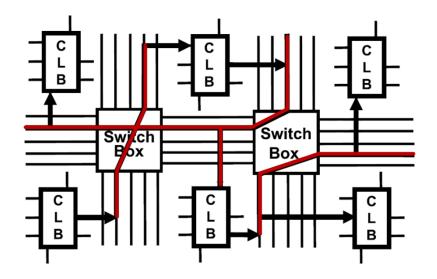

| Figure 2-5  | FPGA Interconnect Architecture. Programmable connections to and out from the CLBs.                                                                                                                                                                                                                                    |    |  |

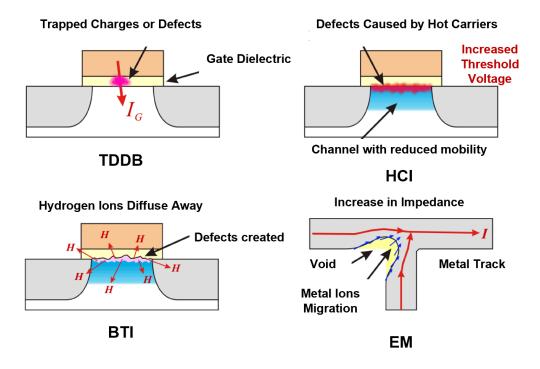

| Figure 2-6  | The Degradation Mechanisms impacting the FPGA reliability                                                                                                                                                                                                                                                             | 33 |  |

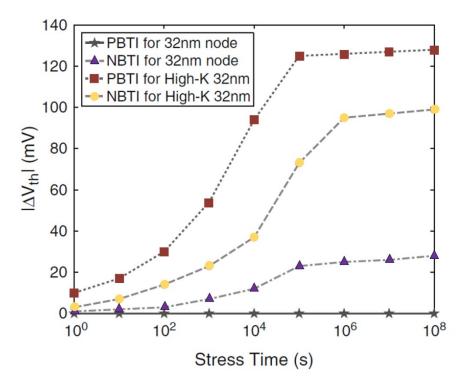

| Figure 2-7  | Shift in Threshold Voltage $\Delta V_{th}$ with high- $\mbox{\it K/M}$ etal gates is becoming significant                                                                                                                                                                                                             |    |  |

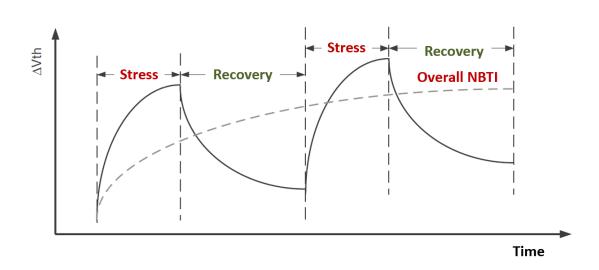

| Figure 2-8  | BTI-induced variations in $V_{th}$ during the stress and recovery period                                                                                                                                                                                                                                              |    |  |

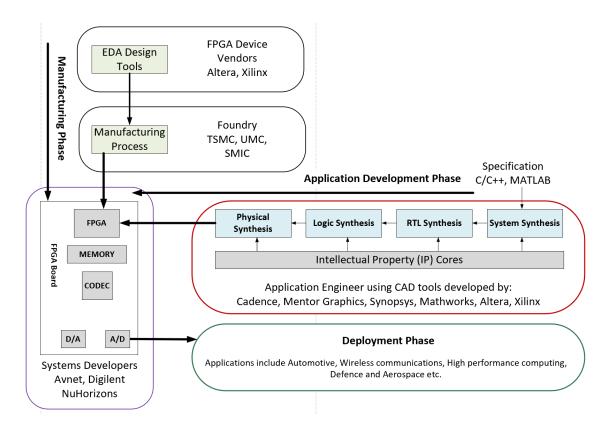

| Figure 2-9  | FPGA Lifecycle – Manufacturing to Application Development to Final Deployment. Handled by several sources using a diverse range of design gadgets. Every phase of the FPGA lifecycle is prone to security threats that need to be collectively addressed to ensure and uphold the device and system reliability.      |    |  |

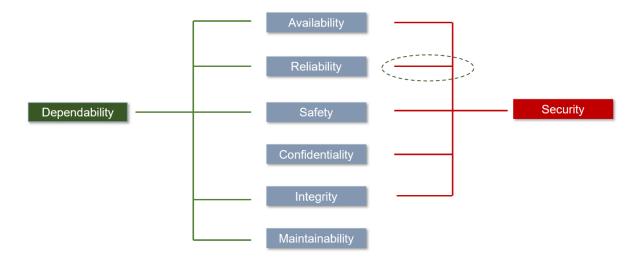

| Figure 2-10 | Dependability and Security Attributes of an FPGA                                                                                                                                                                                                                                                                      |    |  |

| Figure 2-11 | An integrated approach towards Reliability, Prognostics, and Security in FPGAs to bolster FPGA health for high-end Computational Systems.                                                                                                                                                                             |    |  |

| Figure 3-1  | The Disposition of Chapter-3.                                                                                                                                                                                                                                                                                         |    |  |

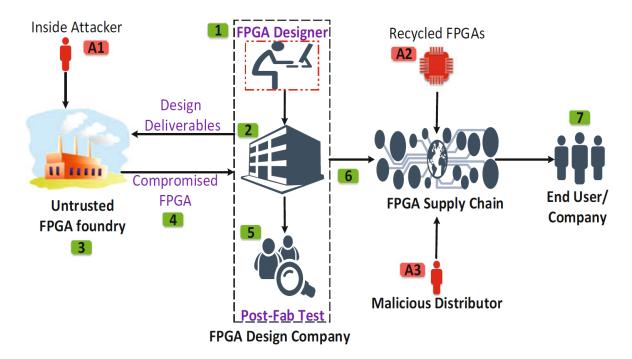

| Figure 3-2  | FPGA threat model: The attacker can insert hardware Trojans at the untrusted foundry (A1). A malicious distributor can reduce the reliability of an FPGA in the supply chain (A3), and even recycled FPGAs can be inserted into the FPGA supply chain (A2). Design Trojans can also enter through FPGA CAD tool flow. |    |  |

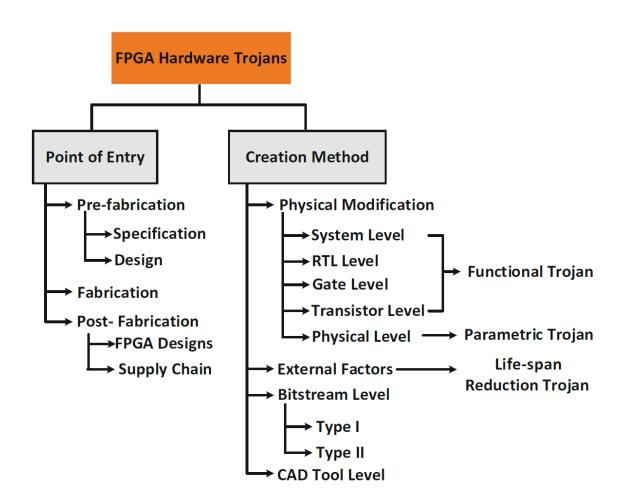

| Figure 3-3  | FPGA hardware Trojan taxonomy based on two primary attributes.                                                                                                                                                                                                                                                        |    |  |

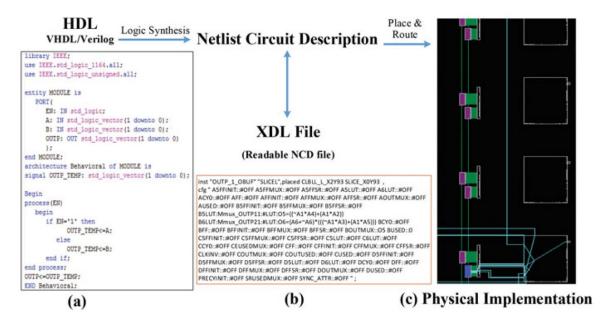

| Figure 3-4  | HDL to FPGA physical implementation. (a) Description of the design in HDL. (b) The configuration of a routed CLB described in XDL format. Only LUT B is used in this CLB. (c) The physical implementation of the design                                                                                               | 74 |  |

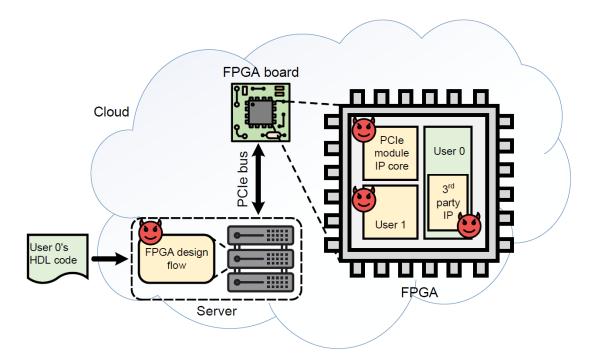

| Figure 3-5  | Architecture of an FPGA in the cloud. The four different threat models considered in this paper are (1) malicious cloud providers, (2) malicious co-tenants, (3) malicious IP providers, and (4) malicious FGPA toolchain. These are indicated in the figure by devil icons in the shell (PCIe module and IP core), user 1's logic, 3rd party IP core, and the FPGA design flow, respectively.                                 |     |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

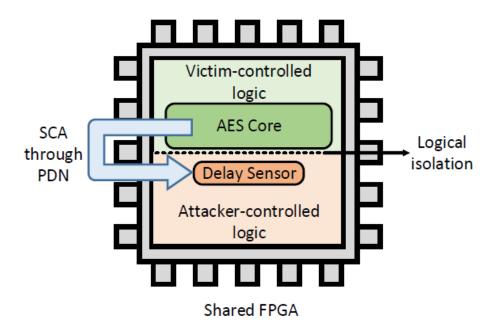

| Figure 3-6  | Remote power analysis attack for a multi-tenant FPGA. The side-<br>channel analysis (SCA) is performed through the power distribution<br>network (PDN) in spite of the logical isolation between the victim logic<br>and the sensor.                                                                                                                                                                                           |     |  |

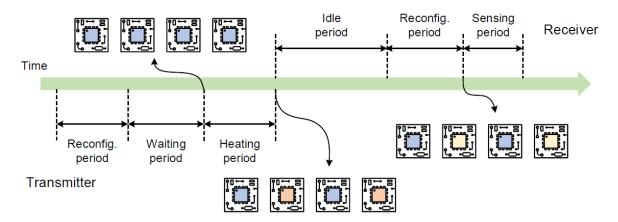

| Figure 3-7  | Establishment of thermal covert channel on cloud FPGA [34]. The transmitter uses 4 FPGAs simultaneously and sends the binary string 0101 in this example. The orange colour of the FPGAs after the heating period represents high temperature. The yellow colour of the FPGAs after the reconfiguration period on the receiver side represents a temperature higher than the un-heated FPGAs, but lower than the heated FPGAs. | 81  |  |

| Figure 4-1  | The Disposition of Chapter 4.                                                                                                                                                                                                                                                                                                                                                                                                  | 91  |  |

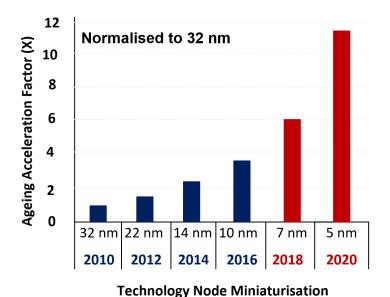

| Figure 4-2  | VLSI Ageing Vs Technology miniaturisation [2]                                                                                                                                                                                                                                                                                                                                                                                  |     |  |

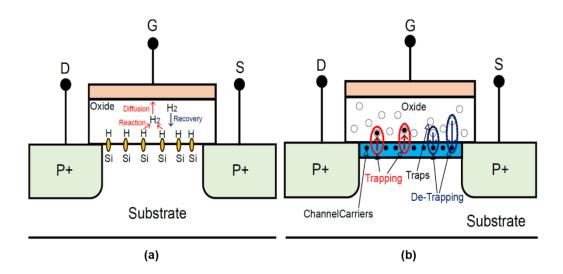

| Figure 4-3  | Depiction of BTI Mechanisms. (a) Reaction-Diffusion (RD) Mechanism. (b) Trapping-Detrapping (TD) Mechanism.                                                                                                                                                                                                                                                                                                                    | 97  |  |

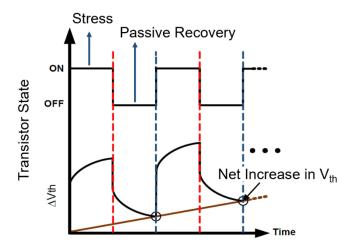

| Figure 4-4  | Dynamic BTI behaviour modelling based on TD mechanism. Net increase in threshold voltage $V_{\text{th}}$ is observed despite passive recovery                                                                                                                                                                                                                                                                                  |     |  |

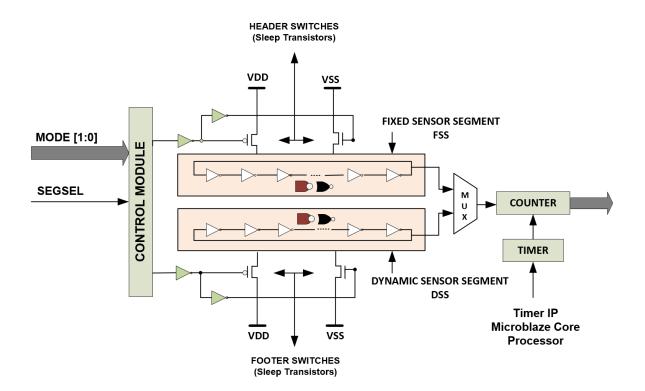

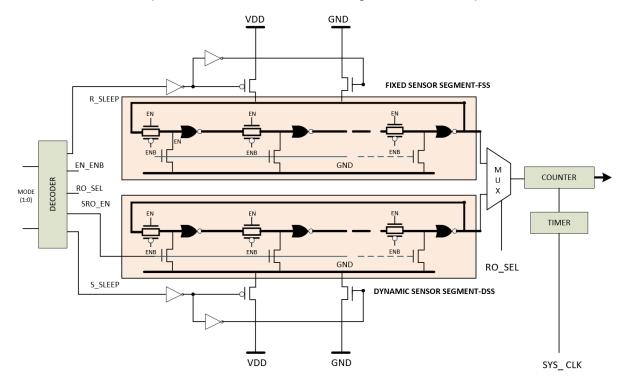

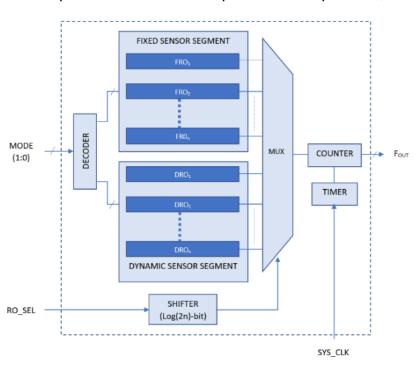

| Figure 4-5  | The Architecture of FREquency Degradation (FRED) Detection and Measurement Sensor.                                                                                                                                                                                                                                                                                                                                             |     |  |

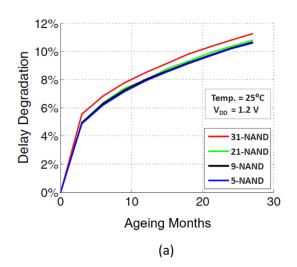

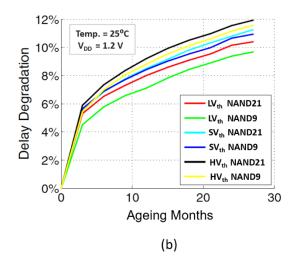

| Figure 4-6  | Degradation of NAND gate (as Sensor Segment) with (a) different number of stages and (b) different threshold voltage levels.                                                                                                                                                                                                                                                                                                   |     |  |

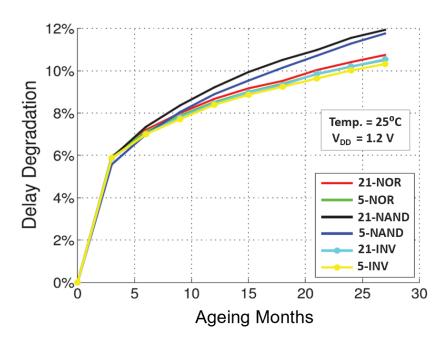

| Figure 4-7  | Degradation pattern of different gate configurations.                                                                                                                                                                                                                                                                                                                                                                          |     |  |

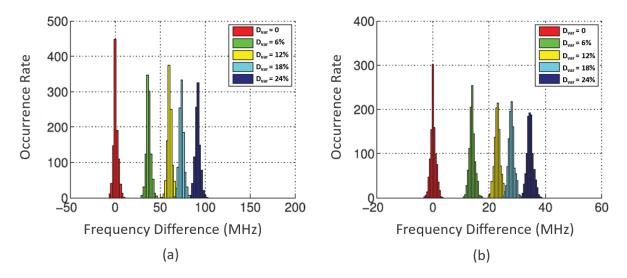

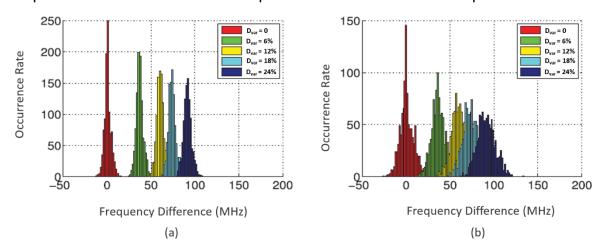

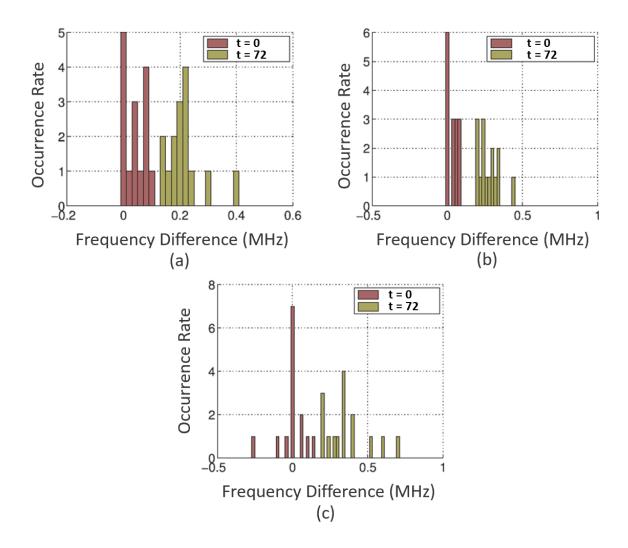

| Figure 4-8  | Frequency Difference distribution of the FRED sensor with $PV_a$ employing (a) 9-Stage Sensor Segments and (b) 21-Stage Sensor Segments.                                                                                                                                                                                                                                                                                       |     |  |

| Figure 4-9  | Frequency Difference ( $f_{\it diff}$ ) distribution of a 21-Stage FSS and DSS segment sensor with: (a) PV <sub>b</sub> and the temperature of 80°C and (b) PV <sub>c</sub> , and a temperature of 110°C                                                                                                                                                                                                                       |     |  |

| Figure 4-10 | A Simplistic Frequency and Delay Measurement Process Flow                                                                                                                                                                                                                                                                                                                                                                      | 109 |  |

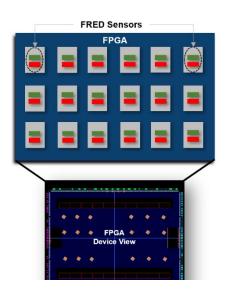

| Figure 4-11 | 28nm FPGA Floorplan showing the spread of 18 FRED sensors implemented to capture Frequency/Delay shifts under varying Thermal and Voltage Stress Conditions.                                                                                                                       |     |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

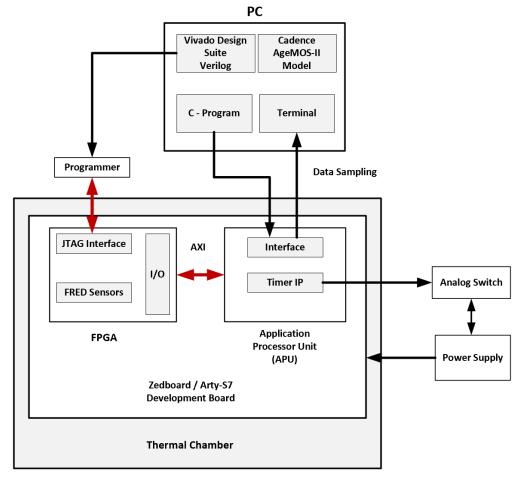

| Figure 4-12 | FRED Sensor Experimentation Setup and Auto-Test Flow                                                                                                                                                                                                                               |     |

| Figure 4-13 | Frequency Difference Distribution – (a) 9-Stage Sensor Segment – 450MHz. (b) 21-Stage Sensor Segment – 300MHz. (c) 31-Stage Sensor Segment – 200MHz                                                                                                                                |     |

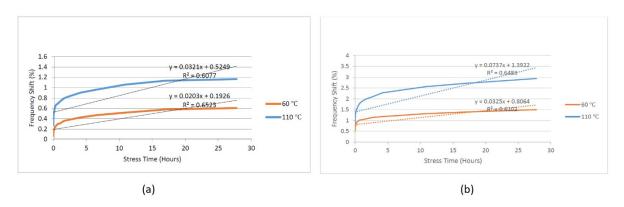

| Figure 4-14 | Percent Frequency Degradation with High Temperature. (a) NBTI AC Frequency Degradation (%) and (b) PBTI AC Frequency Degradation (%).                                                                                                                                              |     |

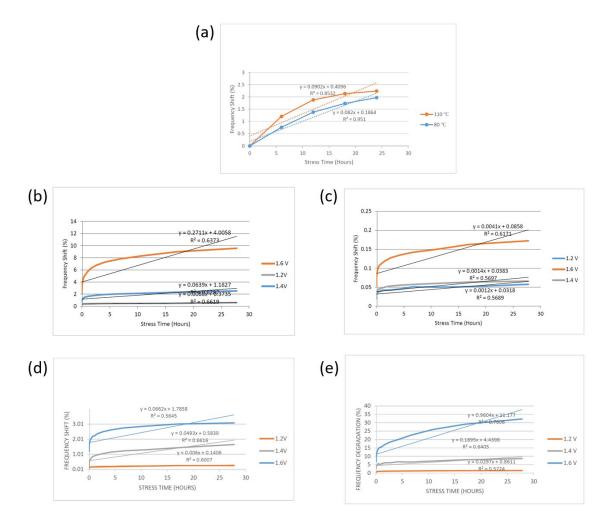

| Figure 4-15 | (a) AC Frequency Degradation (%) with N/PBTI. (b) PBTI Frequency Degradation (%) under AC Stress. (c) NBTI Frequency Degradation (%) under AC Stress. (d) NBTI Frequency Degradation (%) under DC Stress. (e) PBTI Frequency Degradation (%) under DC Stress.                      |     |

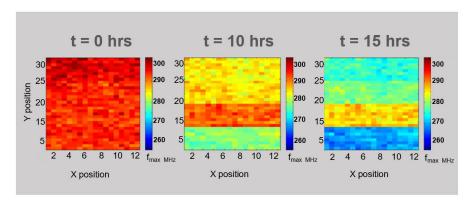

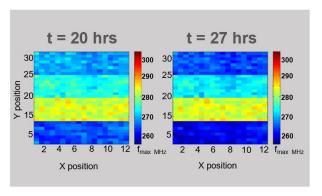

| Figure 4-16 | Frequency Colour Map of 28nm FPGA using FRED Sensor Under Stressed Temperature and Bias Conditions.                                                                                                                                                                                | 117 |

| Figure 5-1  | The Disposition of Chapter 5.                                                                                                                                                                                                                                                      | 126 |

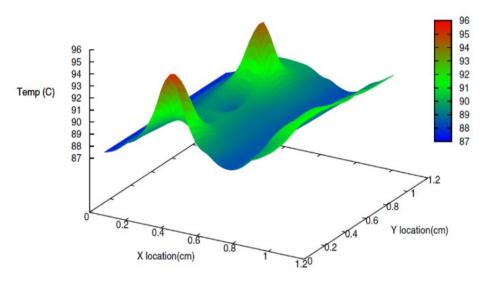

| Figure 5-2  | Thermal profile depicting hotspots in an FPGA                                                                                                                                                                                                                                      | 127 |

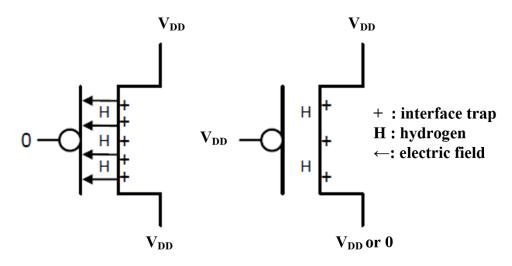

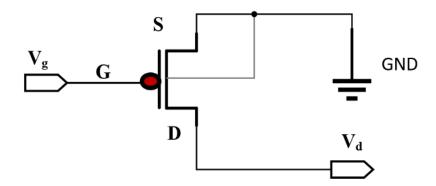

| Figure 5-3  | NBTI mechanism in a PMOS transistor.                                                                                                                                                                                                                                               |     |

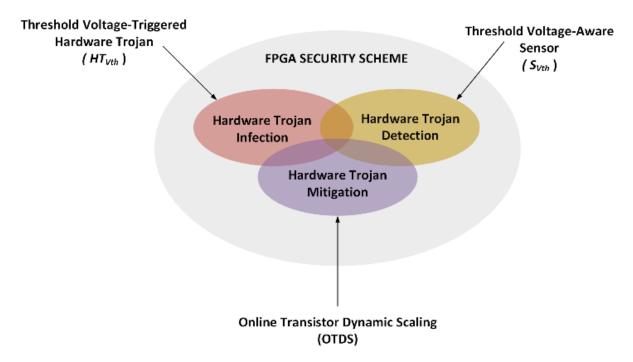

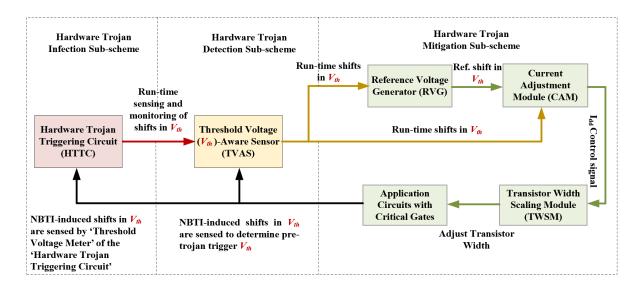

| Figure 5-4  | FPGA Security Scheme comprising hardware Trojan Infection, Detection, and Mitigation sub-schemes.                                                                                                                                                                                  |     |

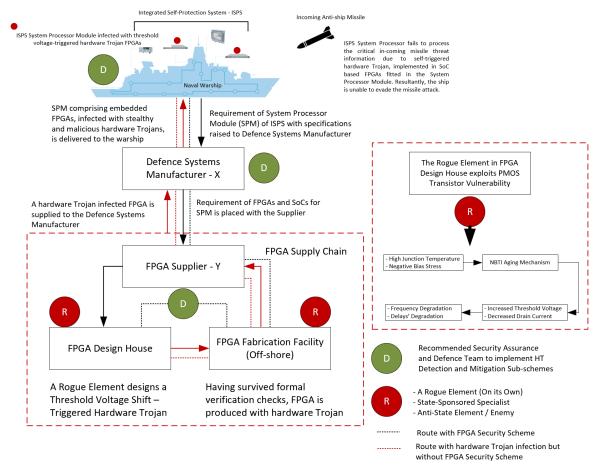

| Figure 5-5  | Threat Model: A novel self-triggered Threshold Voltage-Shift based Hardware Trojan ${}^{\prime}HT_{Vth}{}^{\prime}$ is designed and implemented by a rogue element in a 28 nm FPGA used in System Processor Module of ISPS (Integrated Self Protection System) of a Naval Warship. |     |

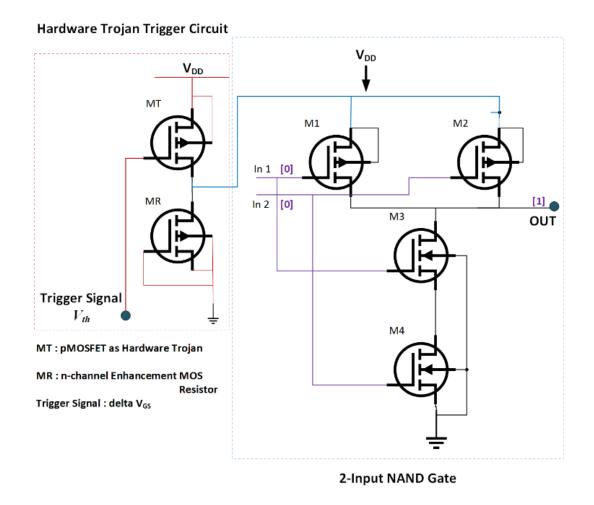

| Figure 5-6  | Schematic of a threshold voltage-triggered hardware Trojan ( $HT_{Vth}$ ) in a combinatorial circuit (2-input NAND gate).                                                                                                                                                          | 140 |

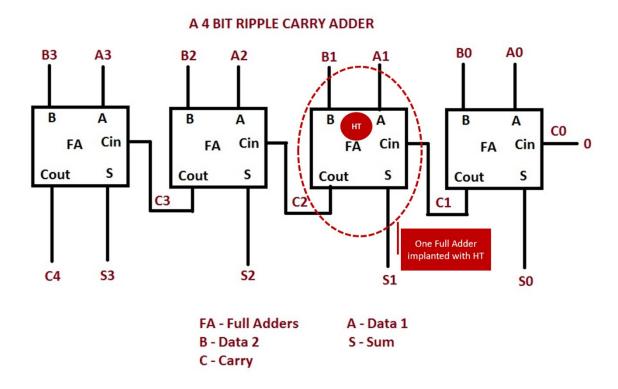

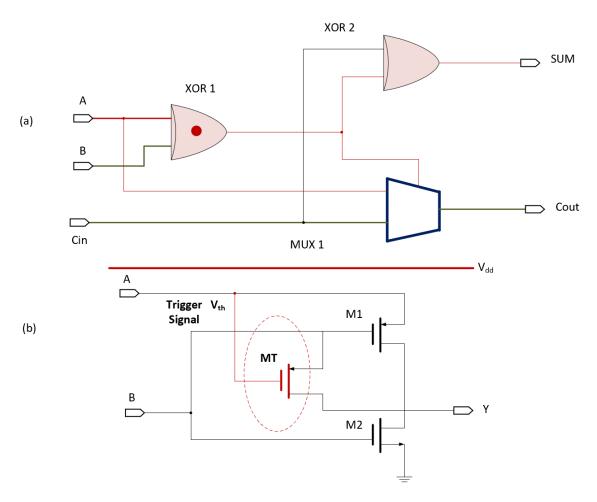

| Figure 5-7  | A block diagram of a 4-BIT ripple carry adder. Full adder with C1 is implanted with a threshold-voltage shift triggered hardware Trojan                                                                                                                                            |     |

| Figure 5-8  | (a) Gate level diagram of Full Adder with XOR1 implanted with hardware Trojan, represented by a red dot. (b) Transistor level circuit of XOR gate with malicious transistor (MT) that receives V <sub>th</sub> trigger at its gate.                                                |     |

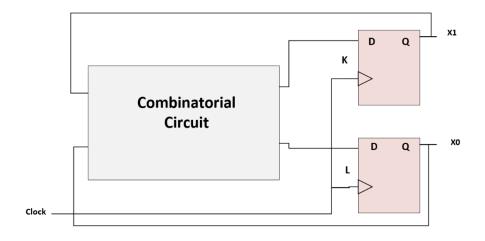

| Figure 5-9  | Block diagram representation of a sequential circuit                                                                                                                                                                                                                               | 143 |

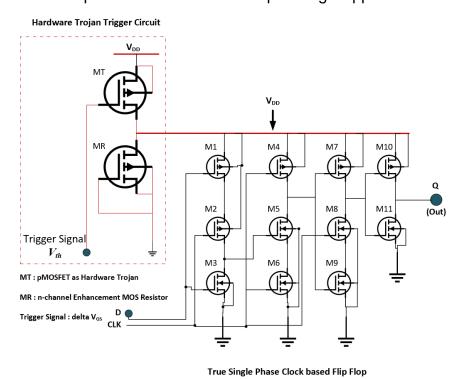

| Figure 5-10 | Schematic of threshold voltage-triggered hardware Trojan in a Sequential Circuit (TSPC based Flip Flop).                                                                                                                                                                           |     |

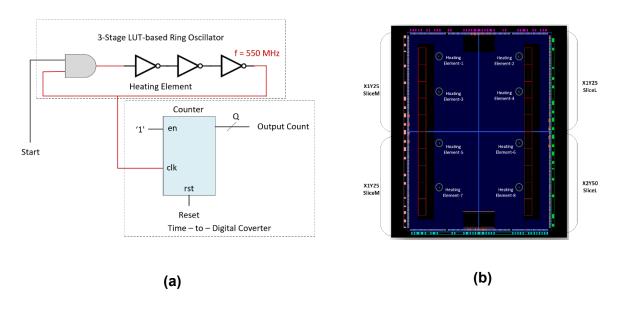

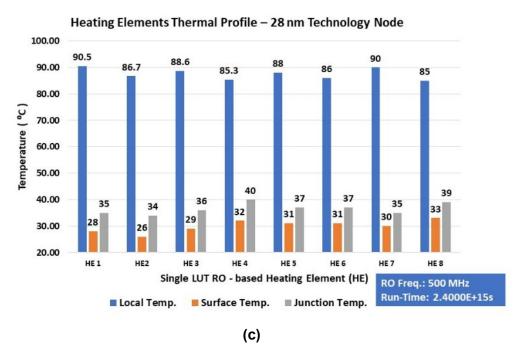

| Figure 5-11 | (a) Schematic of a 3-stage Ring Oscillator-based heating element with Time-to-Digital Converter. (b) 28 nm technology node floor-planned                                                                                                                                           | 145 |

|             | with 08 x heating elements. (c) Thermal profile of FPGA (28 nm technology node) with 08 x heating elements.                                                                                                                                                                                                                                                                                                   |     |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

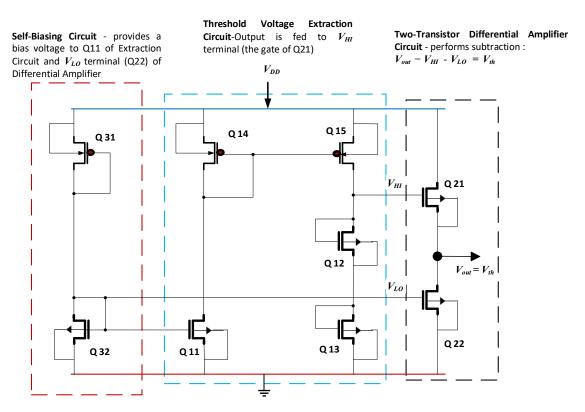

| Figure 5-12 | Schematic of Threshold Voltage Meter. The output of the Differential Amplifier is the Threshold Voltage $(V_{th})$                                                                                                                                                                                                                                                                                            | 147 |  |

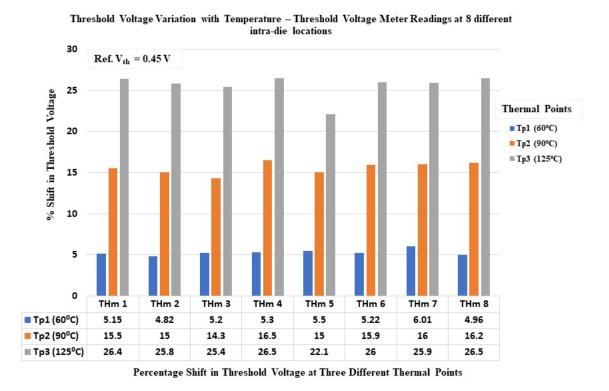

| Figure 5-13 | % Shift in threshold voltage with rise in temperature across 8 different intra-die locations. Threshold voltage meter is used to read $V_{th}$ . Reference $V_{th}$ is pre-defined at 0.45V.                                                                                                                                                                                                                  |     |  |

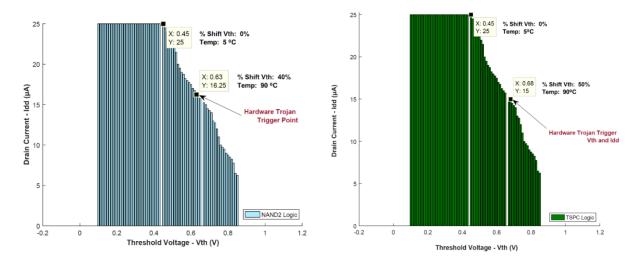

| Figure 5-14 | (Left) An increase of 40% shift in threshold voltage at 90°C degrades the drain current by 35%, triggers the hardware Trojan and impairs the NAND2 logic. (Right) An increase of 50% shift in threshold voltage at 90°C degrades the drain current by 40%, triggers the hardware Trojan and impairs the TSPC logic.                                                                                           | 149 |  |

| Figure 5-15 | The architecture of Threshold Voltage-Aware Sensor.                                                                                                                                                                                                                                                                                                                                                           | 153 |  |

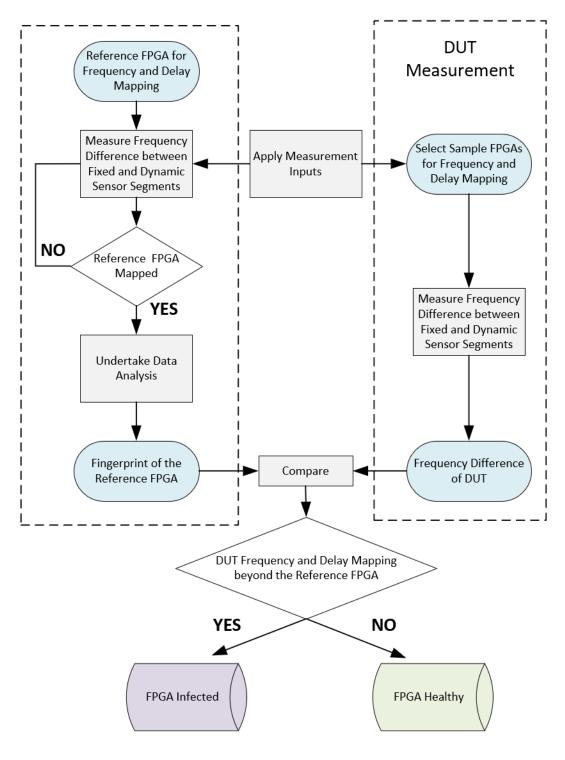

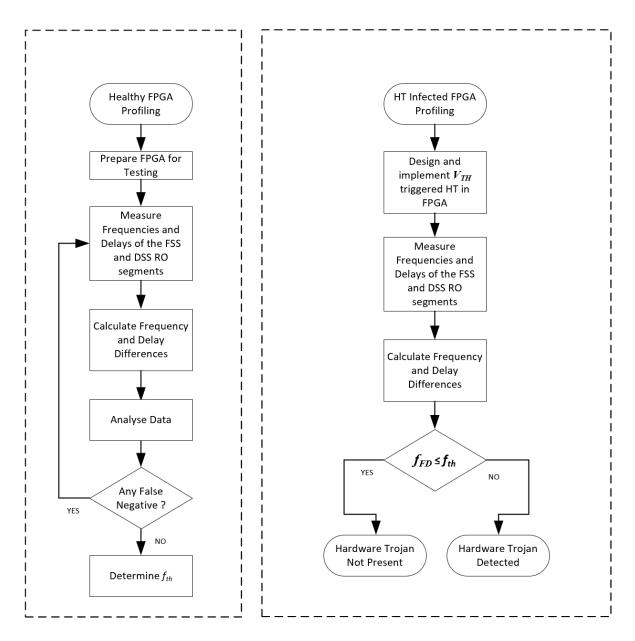

| Figure 5-16 | Process flows for the identification, authentication, and assessment of Trojan-free and Trojan-infected FPGAs using frequency and delay mapping method.                                                                                                                                                                                                                                                       |     |  |

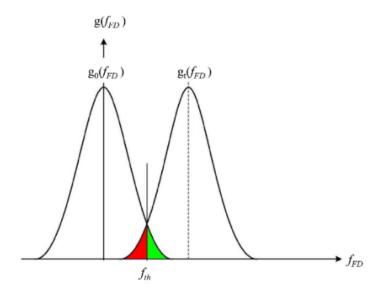

| Figure 5-17 | Probability density function $f_{FD}$ at times 0 $g_0(f_{FD})$ and t $g_t(f_{FD})$                                                                                                                                                                                                                                                                                                                            | 156 |  |

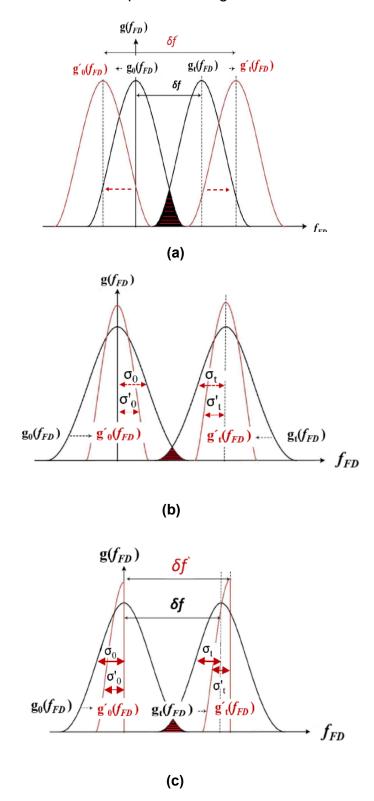

| Figure 5-18 | Reduction of false prediction - represented by the overlapped area. (a) Moving the FSS and DSS distributions away from their respective positions.(b) Minimizing their spread. (c) Minimal spread with a shift of the mean of FSS and DSS distributions.                                                                                                                                                      |     |  |

| Figure 5-19 | Threshold Voltage-aware sensor with enhanced detectability of hardware Trojan due to additional RO pairs architecture.                                                                                                                                                                                                                                                                                        | 159 |  |

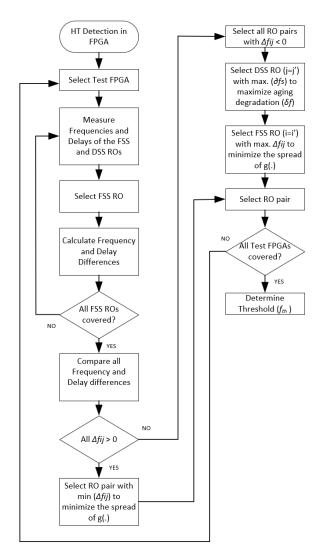

| Figure 5-20 | Process flow for enhanced detectability of hardware Trojan using optimum-performing RO pairs' selection strategy.                                                                                                                                                                                                                                                                                             | 161 |  |

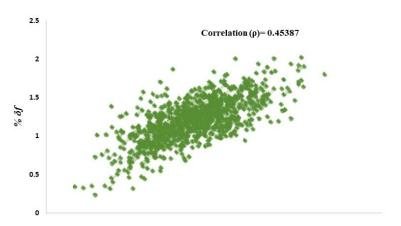

| Figure 5-21 | Scatter plot of correlation between dynamic frequency degradation (% $\delta f$ ) and percentage frequency difference (% $\partial f_{t DSS}$ ) of DSS ROs                                                                                                                                                                                                                                                    | 162 |  |

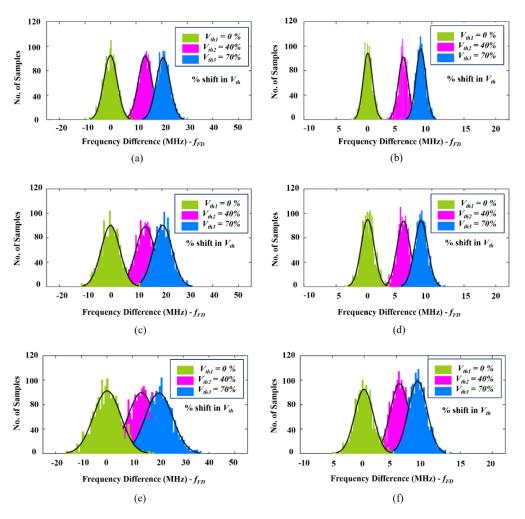

| Figure 5-22 | Distribution of frequency differences between FSS and DSS, $f_{FD}$ , with percentage shifts in threshold voltage in the presence of process variations $PV_a$ , $PV_b$ , and $PV_c$ and changing number of RO stages (9 and 31) in sensor segments. (a) $PV_a$ : 9-stage RO, (b) $PV_a$ : 31-stage RO, (c) $PV_b$ : 9-stage RO, (d) $PV_b$ : 31-stage RO, (e) $PV_c$ : 9-stage RO, (f) $PV_c$ : 31-stage RO. | 163 |  |

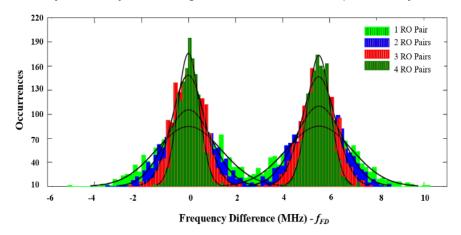

| Figure 5-23 | Gaussian distribution of frequency difference 'fFD' at PVc of Vth-aware sensor with different number of RO-pairs                                                                                                                                                                                                                                                                                              | 164 |  |

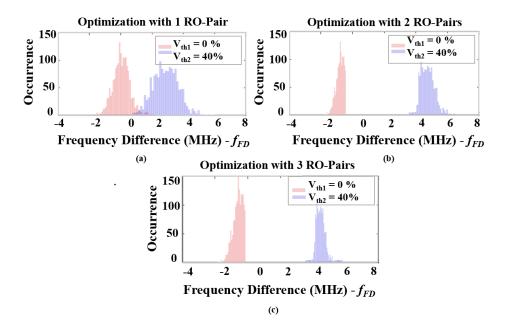

| Figure 5-24 | Histograms of frequency difference distribution $f_{FD}$ at $PV_c$ of $V_{th}$ -aware sensor with different number of RO-pairs. (a) Optimization with 1RO-pair. (b) Optimization with 2 RO-pairs. (c) Optimization with 3 RO-pairs.                                                                                                                                                                           | 167 |  |

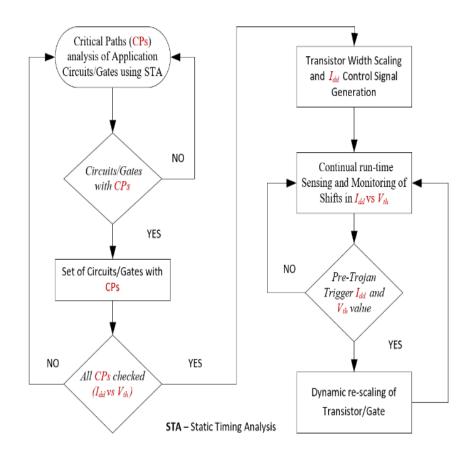

| Figure 5-25 | Block diagram representation of FPGA security scheme highlighting hardware Trojan mitigation sub-scheme.                                                                                                                                                                                                                                                                                                      | 169 |  |

| Figure 5-26 | The Process Flow of Hardware Trojan Mitigation Scheme 1                                                                                                            |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

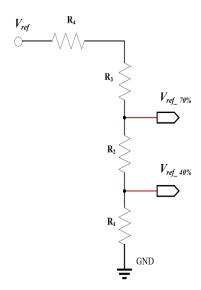

| Figure 5-27 | Resistive Voltage Divider for Reference Voltage Generator (Rvg)                                                                                                    |  |  |

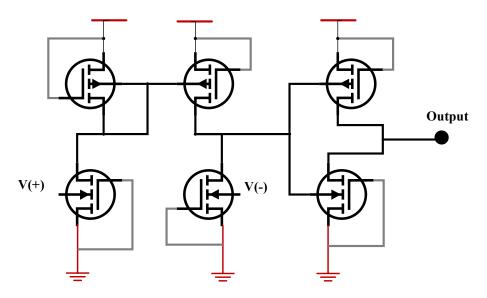

| Figure 5-28 | A Comparator circuit with current-mirror based differential amplifier.                                                                                             |  |  |

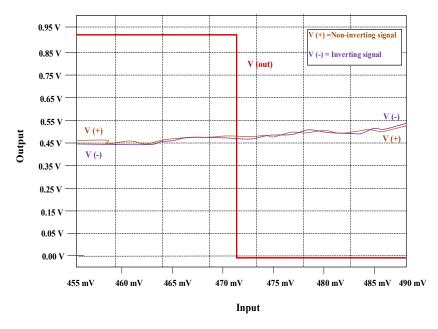

| Figure 5-29 | Input / Output Response of a Comparator.                                                                                                                           |  |  |

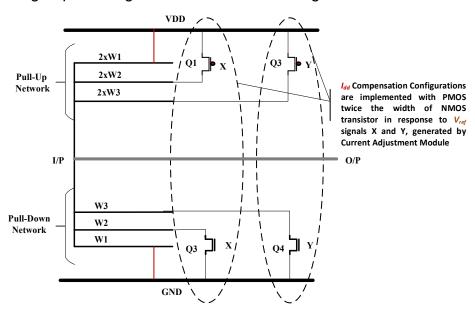

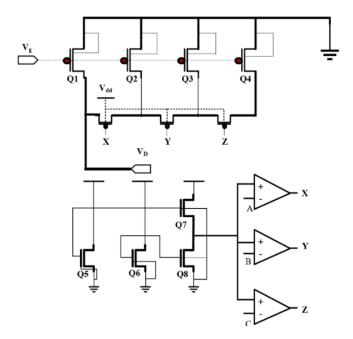

| Figure 5-30 | Online Transistor Dynamic Scaling using Pull-Up and Pull-Down Networks.                                                                                            |  |  |

| Figure 5-31 | Figure 5-31. Circuitry for Transistor Width Parametric Analysis.                                                                                                   |  |  |

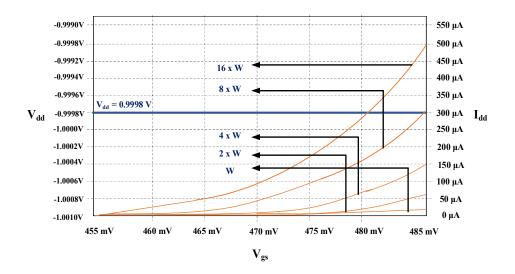

| Figure 5-32 | $I_{\text{dd}}$ vs $V_{\text{gs}}$ Curves Showing Online Transistor Width Increment to Compensate for Threshold Voltage-Triggered Hardware Trojan (Htvth ) Attack. |  |  |

| Figure 5-33 | Threshold voltage-triggered hardware Trojan mitigation circuitry of 'HT-Mitigation Scheme'                                                                         |  |  |

| Figure 6-1  | The Disposition of Chapter 6.                                                                                                                                      |  |  |

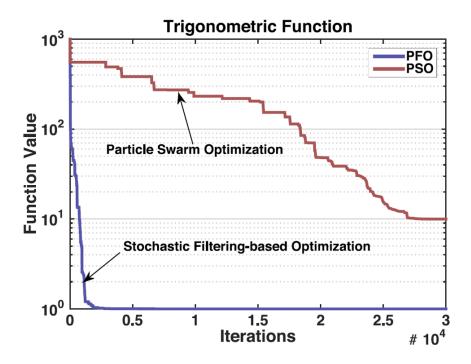

| Figure 6-2  | A comparison of Optimisation Method based on Stochastic Filtering with Particle Swarm Optimisation using a problem related to benchmark optimisation.              |  |  |

| Figure 6-3  | Optimization of hyperparameters using Particle Filtering Approach.                                                                                                 |  |  |

| Figure 6-4  | Kernel-based FPGA Health Estimation Algorithm.                                                                                                                     |  |  |

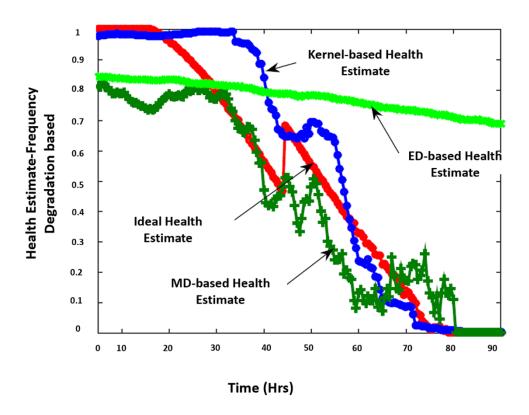

| Figure 6-5  | Results of FPGA Health Estimation for Parametric Deviation (Frequency Degradation of RO-based Sensor Segments) in Combinatorial Circuit (NAND2).                   |  |  |

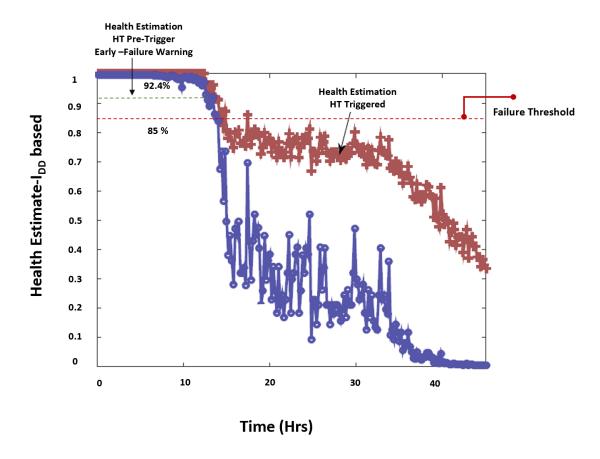

| Figure 6-6  | FPGA Health Estimate with Early-Warning Indication using Kernel 2 Method in a Sequential Circuit configuration.                                                    |  |  |

### **LIST OF TABLES**

| Table 2-1  | Portfolio of post-manufacturing reliability tests conducted by FPGA Manufacturers                                          | 37  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| Table 4-1  | Process variations profile for inter and intra process variations                                                          |     |  |  |

| Table 4-2  | Thermal and Voltage Stress Test Conditions                                                                                 |     |  |  |

| Table 4-3  | A Comparison of FRED Sensor with Other Sensor Designs – Resource Utilisation                                               |     |  |  |

| Table 4-4  | A Comparison of FRED Sensor 'Sensitivity' with Other Sensor Designs.                                                       | 118 |  |  |

| Table 4-5  | Comparison of the Normalised Area and Power Overheads of Four different RO Segment configurations                          | 119 |  |  |

| Table 4-6  | A Normalised Comparison of the Quality Factor of NOR and NAND Sensor Segment Configurations for Different Segment Lengths. | 120 |  |  |

| Table 5-1  | Impact of NBTI aging mechanism on PMOS transistor parameters.                                                              | 137 |  |  |

| Table 5-2  | Hardware Trojan Triggering Analysis in NAND2 Logic.                                                                        | 149 |  |  |

| Table 5-3  | Hardware Trojan Triggering Analysis in True Single Phase Clock (TSPC) Logic.                                               | 150 |  |  |

| Table 5-4  | Binary Modes of Operation.                                                                                                 | 153 |  |  |

| Table 5-5  | Intra-die process variations–Transistor length and oxide thickness                                                         | 161 |  |  |

| Table 5-6  | False Prediction Rates (Probability of Error).                                                                             | 163 |  |  |

| Table 5-7  | Mean and Variance Frequency Distribution of Threshold Voltage Aware Sensor.                                                | 164 |  |  |

| Table 5-8  | Analysis of False Prediction – Improving Sensor Accuracy with RO-pairs scaling and selection process.                      | 166 |  |  |

| Table 5-9  | Area Overhead Analysis of Threshold Voltage-Aware Sensor (S <sub>vth</sub> ).                                              | 167 |  |  |

| Table 5-10 | Measured values – PMOS $I_{dd}$ reduction with increase in $V_{th}$ .                                                      | 175 |  |  |

| Table 5-11 | Measured values – width increment (Fanout-4) with shifts in $V_{\text{th}}$ .                                              | 176 |  |  |

| Table 5-12 | Timing delays in TSPC due to $V_{\text{th}}$ -triggered hardware Trojan payload.                                           | 177 |  |  |

| Table 5-13 | Area and Power consumption comparison of the proposed Threshold Voltage $(V_{th})$ -shift based HT Mitigation Scheme.      | 178 |  |  |

| Table 6-1 | Critical Components of LUT-based Combinatorial Circuit with Nominal, Tolerance and Threshold Values.                       | 201 |

|-----------|----------------------------------------------------------------------------------------------------------------------------|-----|

| Table 6-2 | Performance Analytics of the Developed Health Estimation/Prognostics Method for FPGA – LUT Primitive (NAND2 Application)   | 203 |

| Table 6-3 | Critical Components of LUT-based Sequential Circuit with Nominal, Tolerance and Threshold Values.                          | 206 |

| Table 6-4 | Performance Analytics of the Developed Health Estimation/Prognostics Method for FPGA – LUT Primitive (TSPC-FF Application) | 207 |

| Table 6-5 | A Simplistic Excerpt of FPGA Fault Dictionary – (LUT- TSPC FF)                                                             | 210 |

### **LIST OF EQUATIONS**

| (2-1) | 40  |

|-------|-----|

| (2-2) | 40  |

| (4-1) | 98  |

| (4-2) | 98  |

| (4-3) | 98  |

| (4-4) | 11  |

| (4-5) | 119 |

| (4-6) | 120 |

| (5-1) | 150 |

| (5-2) | 150 |

| (5-3) | 160 |

| (5-4) | 16  |

| (6-1) | 190 |

| (6-2) | 19  |

| (6-3) | 19  |

| (6-4) | 194 |

| (6-5) | 194 |

| (6-6) | 199 |

| (6-7) | 199 |

| (6-8) | 199 |

| (6-9) | 190 |

| (6-10) | 196 |

|--------|-----|

| (6-11) | 196 |

| (6-12) | 196 |

| (6-13) | 202 |

#### LIST OF ABBREVIATIONS

AC Alternating Current

ACAP Adaptive Compute Acceleration Platform

ASIC Application Specific Integrated Circuit

BTI Bias Temperature Instability

CLB Configuration Logic Block

CPS Cyber Physical Systems

CPU Central Processing Unit

DoE Design of Experiment

EM Electromigration

FIT Failure In Time

FPGA Field Programmable Gate Array

FFT Fast Fourier Transform

HCI Hot Carrier Injection

HT Hardware Trojan

IFHM Integrated FPGA Health Management

IC Integrated Circuit

IOB Input Output Block

LUT Look Up Table

NBTI Negative Bias Temperature Instability

NFET Negative Field Effect Transistor

NMOS Negative Metal Oxide Semiconductor

NoC Network on Chip

PBTI Positive Bias Temperature Instability

PFET Positive Field Effect Transistor

PMOS Positive Metal Oxide Semiconductor

PV Process Variation

PHM Prognostics and Health Management

RUL Remaining Useful Life

SRAM Static Random Access Memory

TDDB Time Delay Dielectric Breakdown

VLSI Very Large Scale Integration

#### 1 INTRODUCTION

#### 1.1 Motivation

The evolutionary progression of 'Field Programmable Gate Arrays' (FPGAs), from the traditional architectures to more complex and functionally capable heterogeneous platforms like 'System-on-Chip (SoC)' and 'Adaptive Compute Acceleration Platform (ACAP)' has been phenomenal. This reconfigurable class of integrated circuits is enabling real-time Al inference and adaptive compute acceleration in numerous sensitive applications across wide-ranging industrial sectors [1]. Recent statistical surveys envisage the global FPGA market to reach USD 14.2 billion by 2024 [2]. Against this backdrop, the functional as well as the operational reliability of these miniaturized nano-systems becomes highly relevant and worth probing. More importantly, with the episodes of Meltdown and Spectre casting shadows on the security fabric of FPGAs [3,4] and the vulnerability of its supply chain to hardware threats like hardware Trojans; the safe operation, confidentiality of the sensitive data and reliable performance of FPGAs may be jeopardised. For instance, when deployed in aerospace and defence systems operating under harsh environmental conditions for prolonged duration, the continual health assessment of FPGAs coupled with security is highly desired.

#### 1.1.1 Research Gaps

## 1.1.1.1 Lack of Integrated Approach and Framework for FPGA Health Management

The systematic literature review has revealed that the researchers and academicians have been treating the vital elements of security and reliability in FPGAs as two separate entities [5], [6], [7], [8], [9], [10]. Such an approach is fragmented in nature and does not provide complete health assessment of an FPGA device, which is essential for the optimal functioning and operation of existing and future industrial, health-care, aerospace, and energy systems.

Instead, this has led to a clutter of non-composite solutions which do not provide an effective methodology and framework to build trust and ensure reliability as well as health management in FPGAs. Hence, to meet this challenge, there is a requirement of not only an in-depth study and pragmatic research on these two vital domains in a

composite manner but to formulate a high-level integrated FPGA health management framework.

#### 1.1.1.2 Lack of Design for Prognostics and Security in FPGAs

The existing 'Designs for Testability and Manufacturability' are not optimized to assess the remaining useful life (RUL) of an FPGA at a nano-system level. These designs are focused more on performing testability analysis of FPGAs (and other VLSI devices) using different scan design methods such as scan-based logic built-in self-test (BIST) [11] and JTAG boundary scan, which are themselves vulnerable to hardware attacks [12], [13]. They are not designed and optimised to provide the prognostics and security assessments through a controllable built-in mechanism.

Especially, in the event of a hardware Trojan attack that may accelerate the ageing process (with subsequent delay degradation) in an FPGA (triggered by Negative Bias Temperature Instability - NBTI) [14], its health estimation that encompasses both the prognostics and security elements becomes critically essential. It is, therefore, deemed essential to bridge this gap and build 'Design for Prognostics and Security' that augments the controllability and observability regime in FPGAs for a highly reliable and security-hardened performance.

## 1.1.1.3 Frequency/Delay Degradation Measurement Sensors are Resource-intensive

Intra-die/process variation, which causes performance inconsistency across different process technologies of FPGAs (90nm to 7nm), is a greater challenge. In particular, the literature confirms that the degradation mechanisms of Bias Temperature Instability (BTI) (consisting of Negative and Positive components - NBTI and PBTI), Hot Carrier Injection (HCI), Electromigration (EM) and Time Delay Dielectric Breakdown (TDDB) continue to pose reliability, ageing and performance issues with shrinking process technologies (28nm and below). This can be exploited by a rogue element to design and implement hardware Trojan to de-functionalise FPGA and affect the systems' performance [14]. One of the key performance parameters that is highly sensitive to process variation and is the direct consequence of N/PBTI mechanisms is the propagation delay, which is the function of frequency degradation, threshold voltage shift, and reduction in the drain current – the device ageing parameters. In other words, delays are the function of transistors' ageing. Therefore, precise

measurement of these critical transistor parameters propagation delays of arbitrary signal paths through logic blocks, interconnects and heterogeneous elements on an FPGA, is critical for the accurate prediction of its performance.

The evidence from literature reveals that the existing propagation delay measurement sensors and methods are largely based on synchronous (using system clocks) designs and suffer from performance issues, namely clock jitter and flip flop metastability [15]. They consume more FPGA resources and are prone to reliability issues [16]. Therefore, building asynchronous sensor designs and characterising them to utilise in-field timing slack and transition probability measurement methods for determining propagation delay, can help improve the detection of hardware Trojans embedded in FPGA and provide vital parametric data for its health estimation.

#### 1.2 Research Aim and Objectives

#### 1.2.1 Aim

In order to address the above-mentioned research gaps, we defined our overall scientific aim as follows:

'Design for Prognostics and Security in Field Programmable Gate Arrays (FPGAs) that facilitates their reliability and security enhancement, enables NBTI-based hardware Trojan detection and mitigation within their reconfigurable fabric and helps estimate their health'.

#### 1.2.2 Objectives

Based on the above, we defined the following key objectives to achieve the aim:

#### 1.2.2.1 Integrated FPGA Health Management (IFHM) Framework

Devise a high-level integrated framework for FPGA health management that provides guidance to the researcher, an FPGA manufacturer, and an expert end-user on the process flows and methods required to develop a 'Design for Prognostics and Security in FPGAs' in a composite manner.

#### 1.2.2.2 Frequency/Delay Degradation Measurement Sensor

Design and implement a small footprint on-chip sensor (in the target 28 nm FPGA technology node) with low area and power overheads and high sensitivity to detect

frequency degradation and delay variations. Characterise the sensor under nominal and stressed Temperature and Voltage conditions for the variations in frequency, delay, and threshold voltage, followed by collation of data to prognosticate FPGA health.

#### 1.2.2.3 FPGA Security Scheme

Design and implementation of an FPGA Security Scheme capable of detecting a hardware Trojan and providing effective mitigation. It comprises investigation and measurement of the degradation/ageing impact of Negative Bias Temperature Instability (NBTI) on the target FPGA (*resulting in threshold voltage shifts*) by conducting highly accelerated stress tests in a controlled environment. Based on the acquired results and collated data, design and implement Threshold Voltage Shift-triggered HT inside the target FPGA for the payload and detection analysis (*observing threshold voltage shifts, and corresponding frequency degradation and delays*), followed by detailed data analytics to build HT-infected FPGA profile. In addition, the hardware Trojan mitigation scheme would form an integral part of this scheme.

#### 1.2.2.4 FPGA Health Estimation

Develop FPGA health estimation/prognostics method using Kernel-based machine learning technique. The validated data from the healthy and HT-infected FPGA profiling experiments will be used to evaluate the method – resulting in the culmination of the 'Design for Prognostics and Security'.

#### 1.3 Research Methodology

The overall research methodology is constructed around the research objectives. The quantitative research methodology has been adopted and is augmented with the 'Design of Experiment' (DoE) approach for the experimentation phases, followed by the statistical analysis of the validated data. Quality assurance of the project is achieved by ensuring the correctness of the processes developed to conduct design and implementation tests, the collation of experimental data and 'a posteriori' analysis.

The details of research methodology are appended below. In addition, the research methodology process flow is given in Figure 1-1 for a quick overview.

#### 1.3.1 Phase-1

This phase marked the beginning of the research process with the building up of the context of research on 'Reliability & Prognostics in FPGAs' and 'Hardware Security in FPGAs' through literature review. It was aimed at understanding the existing research made to date in the aforementioned areas and excavating gaps that can be worked upon for an intelligible contribution and improvement in the field of FPGA prognostics and health management coupled with security. The main deliverables of this phase were the 'Research Gaps' and the high-level 'Integrated FPGA Health Management (IFHM)' framework.

#### 1.3.2 Phase-2

The research gaps from phase-1 were analysed to develop the requirements for designing and outlining requisite experiments. This phase consisted of two subphases. In the first sub-phase, the functional and operational architectures for the series of experiments, required to develop 'Design for Prognostics and Security in FPGAs', were defined. It included the software and hardware components, their interfacing and optimization to ensure the development of an efficient and effective experimental set-up and test rig. The second sub-phase related to the design and

Figure 1-1 Research Methodology Process Flow Diagram.

implementation of a digital sensor inside the target FPGA, followed by its simulated and real-time testing and characterisation. The main deliverable of this phase was 'FREquency Degradation Detection and Measurement Sensor – FRED'.

#### 1.3.3 Phase-3

This phase was aimed at designing and implementing FPGA Security Scheme. It consisted of the design and implementation of the Threshold Voltage Triggered hardware Trojan in the target FPGA, improving the FRED sensor design for accuracy and to enable detection of shifts in threshold voltage due to NBTI mechanism, building HT-mitigation sub-scheme, and eventually subjecting it to 'Thermal and Power Cycling' under pre-defined stress test conditions. The main deliverable of this phase was the 'FPGA Security Scheme'.

#### 1.3.4 Phase-4

Kernel-based Machine Learning method was studied and evaluated for prognosticating FPGA health in this phase. Accordingly, the method was developed and validated against FPGA fault dictionary. The main deliverable of this phase was the 'FPGA Health Estimation/Prognostics'.

#### 1.4 Organisation of Thesis

This thesis is organised into seven chapters in the 'Paper-Format' and not as a 'Monograph Format' thesis. Accordingly, the papers have been reformatted into chapters with minor changes to maintain coherence and ensure format consistency. The thesis disposition is shown in Figure 1-2. A brief overview of the remaining chapters is given as follows:

#### 1.4.1 Chapter 2

This chapter is the outcome of 'Objective 1' and it delineates the integrated approach to prognostics and security in FPGAs by putting forth an 'Integrated FPGA Health Management (IFHM)' framework. The architecture of a modern FPGA is explained inter alia its commercial and industrial significance. The chapter draws the canvas of the extant and the future technological revolution with FPGAs at the heart of it. Most significantly, it excavates the FPGA reliability issues, vulnerabilities, threats, and several counteractive research efforts made in the realms of FPGA reliability,

prognostics, and security to enhance its dependability and build trust. A high-level framework, called **IFHM** is finally presented that provides guidance on managing prognostics and security in FPGAs as a composite entity for their security and reliability hardening.

This chapter is the reformatted version of the paper under submission to 'IEEE Transactions on Device and Materials Reliability'.

#### 1.4.2 Chapter 3

This chapter highlights the integrated circuit (IC) level threats with an emphasis on hardware Trojans that pose a significant threat to computational systems employing FPGAs, Systems-on-Chip (SoC) or Network-on-Chip (NoC). It describes the hardware Trojan phenomenon, its taxonomy, and gives a critical analysis of various hardware Trojan countermeasures.

This chapter is the reformatted version of the conference paper published in 'Advances in Manufacturing Technology XXXII – 2018'.

Figure 1-2 Thesis Organisation – Disposition of Chapters.

#### 1.4.3 Chapter 4

This chapter is the outcome of '**Objective 2**'. It provides a deep insight into the current research on capturing delay variability in VLSI circuits, including FPGAs. The design and implementation of the FREquency Degradation detection and measurement sensor in a 28 nm process technology is elaborated. In addition, the simulation and real-time experimentation alongwith results and the proposed sensor's performance evaluation are presented.

This chapter is the reformatted version of the paper under submission to **Sensors** journal.

#### **1.4.4 Chapter 5**

This chapter is the outcome of 'Objective 3'. It presents a comprehensive FPGA security scheme, comprising novel elements of hardware Trojan infection, detection, and mitigation, to protect FPGA applications against the hardware Trojan. Built around the threat model of a naval warship's integrated self-protection system (ISPS), this chapter proposes a threshold voltage-triggered hardware Trojan that operates in a threshold voltage region and remains stealthy with a very low area overhead. It delineates the hardware Trojan detection sub-scheme comprising a unique lightweight threshold voltage-aware sensor. An online transistor dynamic scaling (OTDS) to mitigate the impact of hardware Trojan is also presented as a hardware Trojan Mitigation sub-scheme.

This chapter is a reformatted version of the paper published in **IEEE Access** journal.

#### 1.4.5 Chapter 6

This chapter is the outcome of '**Objective 4**'. It proposes an FPGA health estimation method that is developed using a unique kernel-based machine-learning approach. More specifically, this chapter focuses on estimating the health of an FPGA that is degraded as a result of NBTI initiated by hardware Trojans. A stochastic filtering optimization algorithm for accurate hyperparameter selection is also proposed to help improve the overall FPGA health estimation/prognostics accuracy. The chapter later presents the evaluation results of the developed method and the overall accuracy.

This chapter is a reformatted version of the paper under submission to **Microelectronics Reliability** journal.

#### 1.5 List of Published/Submitted Work

#### 1.5.1 Journal Publication

S. Aslam, I. K. Jennions, M. Samie, S. Perinpanayagam and Y. Fang, "Ingress of Threshold Voltage-Triggered Hardware Trojan in the Modern FPGA Fabric–Detection Methodology and Mitigation," in *IEEE Access*, vol. 8, pp. 31371-31397, 2020.

#### 1.5.2 Conference Publication

S. Aslam, M. Samie, I. Jennions; "Hardware Trojans and Smart Manufacturing – A Hardware Security Perspective", Advances in Manufacturing Technology XXXII: proceedings of the 16th International Conference on Manufacturing Research, University of Skövde, Sweden, 11–13 September 2018. (DOI: 10.3233/978-1-61499-902-7-305).

#### 1.5.3 Virtual Conference Presentation

J. Buu-Sao, M. Samie, S. Aslam, et. al., "IoT Security – Hardware Perspective", December 2018, the IoT Day Slam 2018, VIRTUAL Internet of Things Conference: <a href="https://iotslam.com/session/iot-security-hardware-perspective/">https://iotslam.com/session/iot-security-hardware-perspective/</a>.

#### 1.5.4 Under Peer Review for Journal Publication

- S. Aslam, I. Jennions, M. Samie, S. Perinpanayagam, : "Reliability, Security, and Prognostics in FPGAs An Integrated Approach". to: IEEE Transactions on Device and Materials Reliability (under peer review)

- S. Aslam, I. Jennions, M. Samie, S. Perinpanayagam, : "FREquency Degradation (FRED) Detection and Measurement Sensor for Reliable and Secure FPGAs". to: Sensors (under peer review)

- S. Aslam, I. Jennions, M. Samie, S. Perinpanayagam, : "FPGA Health Estimation Using Kernel Learning Approach". to: **Microelectronics Reliability (under peer review)**

#### REFERENCES

- [1] Chino, 'Xilinx Unveils Their Revolutionary Adaptive Compute Acceleration Platform', [Online]. Available at: <a href="https://www.techpowerup.com/242538/xilinx-">https://www.techpowerup.com/242538/xilinx-</a> [Accessed: 15 July 2018].

- [2] Grand View Research, "Field-Programmable Gate Array Market Cruising Ahead," [Online]. Available at: <a href="https://www.grandviewresearch.com/blog/field-programmable-gate-array-fpga-market-size-share">https://www.grandviewresearch.com/blog/field-programmable-gate-array-fpga-market-size-share</a>. [Accessed: July 2020].

- [3] M. Lipp *et al.*, "Meltdown: Reading Kernel Memory from User Space," Commun. ACM 63, pp 46-56, 2020.

- [4] P. Kocher *et al.*, "Spectre Attacks: Exploiting Speculative Execution," *2019 IEEE Symposium on Security and Privacy (SP)*, San Francisco, CA, USA, pp. 1-19, 2019.

- [5] Z. Zhang, Q. Yu, L. Njilla and C. Kamhoua, "FPGA-oriented moving target defense against security threats from malicious FPGA tools," 2018 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), Washington, DC, pp. 163-166, 2018.

- [6] S. Zamanzadeh and A. Jahanian, "Scalable security path methodology: A cost-security trade-off to protect FPGA IPs against active and passive tampers," 2017 Asian Hardware Oriented Security and Trust Symposium (Asian HOST), Beijing, pp. 85-90, 2017.

- [7] Z. Zhang, L. Njilla, C. A. Kamhoua and Q. Yu, "Thwarting Security Threats From Malicious FPGA Tools With Novel FPGA-Oriented Moving Target Defense," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 27, no. 3, pp. 665-678, March 2019.

- [8] P. Maene, J. Götzfried, R. de Clercq, T. Müller, F. Freiling, and I. Verbauwhede, "Hardware-based trusted computing architectures for isolation and attestation," Trans. Comp., vol. 67, no. 3, pp. 361–374, 2018.

- [9] H. Zhang et al., "Architectural support for containment-based security," in Proc. Arch. Supp. Programm. Lang. Op. Sys., pp. 361–377, 2019.

- [10] X. Wang, S. Si, C. Gao and J. Huang, "A method of FPGA interconnect resources testing by using XDL-based configuration," *2014 Prognostics and System Health Management Conference (PHM-2014 Hunan)*, Zhangiiaijie, pp. 203-207, 2014.

- [11] Laung-Terng Wang, Yao-Wen Chang, Kwang-Ting (Tim) Cheng, "Design for testability- Electronic Design Automation", Morgan Kaufmann, pp 97-172, 2009.

- [12] H. B. Shashidhara, S. Yellampalii and V. Goudanavar, "Board level JTAG/boundary scan test solution," *International Conference on Circuits, Communication, Control and Computing*, Bangalore, pp. 73-76, 2014.

- [13] L. Pierce and S. Tragoudas, "Enhanced Secure Architecture for Joint Action Test Group Systems," in *IEEE Transactions on Very Large Scale Integration* (VLSI) Systems, vol. 21, no. 7, pp. 1342-1345, July 2013.

- [14] Bhunia, Swarup, Tehranipoor, Mark M. (Eds.), *The Hardware Trojan War-Attacks, Myths, and Defenses*, Springer International Publishing, DOI 10.1007/978-3-319-68511-3, 2018.

- [15] J. S. J. Wong and P. Y. K. Cheung, "Timing Measurement Platform for Arbitrary Black-Box Circuits Based on Transition Probability," pp. 1–14, 2013.

- [16] Z. Ghaderi, M. Ebrahimi, Z. Navabi, E. Bozorgzadeh, and N. Bagherzadeh, "SENSIBle: A Highly Scalable SENsor DeSIgn for Path-Based Age Monitoring in FPGAs," *IEEE Trans. Comput.*, vol. 66, no. 5, pp. 919–926, 2017.

# 2 UNIFIED FRAMEWORK FOR HEALTH AND SECURITY OF FPGAs

This chapter presents an integrated (unified) approach to prognostics and security in FPGAs by putting forth an 'Integrated FPGA Health Management (IFHM)' framework. It begins with a succinct introduction to the architecture of a modern FPGA, highlights its commercial and industrial significance, and draws the canvas of the extant and the future technological revolution with FPGAs at the heart of it. Sections 2 and 3 excavate the FPGA reliability issues, vulnerabilities, threats, and several counteractive research efforts made in the realms of FPGA reliability, prognostics, and security to enhance its dependability and build trust. A high-level unified framework, called IFHM is then presented in Section-4 that provides guidance on managing prognostics and security in FPGAs as a composite entity for their security and reliability hardening. The conclusion summarises this chapter and briefly outlines the next stage of work. Figure 2-1 depicts the arrangement of this chapter. The main contribution of this chapter besides propounding IFHM framework includes the incisive and critical evaluation of FPGAs' security and reliability realms to uncover the subtleties of this reconfigurable integrated circuit. It is a unique effort, not endeavoured previously.

Figure 2-1 The Disposition of Chapter 2.

#### 2.1 Introduction

From simple Bluetooth devices to the NASA's Orion spacecraft, FPGAs have become the backbone of embedded system design. According to [1], the main driving factors for the exponential growth of the FPGA market are the increasing demand for advanced compute acceleration, autonomous and Al-based systems, the evolution of connectivity network to IoT, institutionalisation of cyber-physical systems (CPS), and the reduction in time-to-market. Through the merger of software and hardware properties, FPGAs provide an effective trade-off between the programmability of CPUs and the performance of application-specific hardware. Even though this flexibility helps developers to speedily prototype and deploy embedded systems with performance closer to Application Specific ICs, the programmability feature could be exploited to eavesdrop on encrypted communication, disrupt critical functionality, or even incur physical damage to the chip. Designing and developing systems that are both flexible and reliable, yet fundamentally sound from a security point of view, is an extraordinarily challenging venture for both researchers and practitioners. Quite often, the security facets of a reconfigurable entity, such as an FPGA, are not catered for until far too late in the design process, resulting in systems that are not reliable and hence, protected only by their obscurity.

#### 2.1.1 The Increased Reliance on FPGAs

FPGAs are a vital element of many mission-critical systems, silently controlling and monitoring everything from wireless access points (WAP) to commercial face recognition systems. According to [1], the FPGA market is expected to reach 117.97 billion US dollars by 2026 growing at the compound annual growth rate (CAGR) of 7.2% during the forecast 2017-2026. This huge surge explains the growing significance of these massively parallel architectures.

As opposed to the sequential execution enabled by a general-purpose processor, modern FPGAs can carry out thousands of multiplies and adds each cycle, providing them the computational power to host numerous diverse logic modules simultaneously. For instance, an FPGA-hosted Wireless Access Point (WAP) application may use a packet scheduler with signal processing core and a protocol processing engine, all sharing the same FPGA primitives and silicon [2].

By virtue of this unique combination of computation power and flexibility, FPGAs are being regarded as the workhorses behind a wide variety of performance critical embedded systems [3]. They are capable of achieving high speedups and performance gain (100x) per unit of area as compared to a similar microprocessor [4]. High-end satellite systems, network-centric warfare equipment, intrusion detection systems, SMART grid, Industrial IoT devices, aircraft and avionics, and even the Mars Rover have great dependence on FPGAs to undertake their respective functional tasks. These devices help implement optimised circuitry for almost everything from encryption to FFTs, or even entire customized multi-processor systems by leveraging their bit-level reconfigurability. A gamut of such different domains leveraging FPGAs is shown in Figure 2-2. In order to understand this growing reliance on FPGAs, we need to examine the internals of the FPGA and its overall architecture.

Figure 2-2 A Gamut of FPGA Applications.

#### 2.1.2 The Internals of FPGA

An FPGA is a mesh of programmable logic gates embedded in a flexible interconnect, as shown in Figure 2-3. These logic gates are implemented by configuring look-uptables (LUTs) for computational applications, flip-flops for managing timing across different applications, switching interconnects for laying routing network, and I/O blocks (IOB) for moving data/signal inside and outside of the FPGA. The logic gates are, basically, the structures with respective truth tables that enable the mapping of any circuit to an FPGA through LUT reconfiguration and by arranging bits in the switchboxes, which then specify the wires' connections through pass transistors. It is pertinent to mention here that the LUT and switchbox are programmed as defined by the configuration bitstream. The security of configuration bitstream, therefore, takes precedence and accordingly three different FPGA structures are commonly used, as shown in Figure 2-4. The ones that use EPROM/EEPROM or antifuse are write-once

Figure 2-3 An architecture of a typical FPGA. The Configuration Logic Blocks (CLBs) are islands with a mesh of programmable interconnects around them. Each CLB houses a Lookup Table (LUT) that can be configured to implement any logic gate.

Figure 2-4 Three Types of FPGAs - SRAM, FLASH, and ANTI-FUSE.

technologies. On the other hand, the re-programmable structures are the Static RAM (SRAM) FPGAs. While a number of architectures make use of antifuse type, **Static RAM (SRAM)** architecture is the most preferred since it allows for reconfiguration – the essence of reconfigurable computing.

The SRAM programming bits are spread across the entire FPGA and stored locally with the LUTs and switchable interconnects. **This increases their vulnerability to probable performance degradations and reliability-downgrade due to undesired distributed hardware attacks.**

#### 2.1.2.1 SRAM FPGA Specifics

Generally, a combination of two inverters and pass transistors is used to develop the Static RAM (SRAM) cells (see Figure 2-3). FPGAs based on SRAM cells are volatile in nature, meaning that as long as the SRAM cell is powered, the data remains stored and can be, therefore, read from the cell. However, as soon as there is no power, SRAM cell is unable to retain its value [5]. This feature offers some security and makes it difficult for the intruder to retrieve the configuration bitstream, thereby helps retain the data integrity.

In SRAM FPGAs, LUTs make optimum use of SRAM cells as programming bits. Healthy condition of LUTs is, therefore, vital to ensure unhindered operation and

Figure 2-5 FPGA Interconnect Architecture. Programmable connections to and out from the CLBs [6].

optimum functioning of the implemented circuit patterns. Also, as seen in Figure 2-3, the LUTs in addition to flip flops, and multiplexers form an integral part of the larger regions, known as configurable logic blocks (CLBs). To connect the configuration and computational blocks together, there is a large routing channel, which is a set of pass transistors, providing programmable connections to and out from the CLBs (see Figure 2-5). The point-to-point connections between neighbouring routing channels containing longlines, on the other hand, are enabled through switchbox network. This complex routing architecture contributes to both the delays and area constraints in the FPGA, if not optimised. It is estimated that 80-90% of the typical FPGA area is occupied by the interconnect, facilitating both the physical wires and the configuration bits that link the wires together for any arbitrary interconnection network [6]. **Despite** the criticality of the interconnect for configurability, it also poses complications in building a secure and reliable FPGA infrastructure.

Keeping these FPGA architectural sensitivities in perspective, we delve the realms of reliability and security to build an integrated FPGA health management framework, in the ensuing sections.

### 2.2 Realm of Reliability in FPGAs

Reliability in FPGAs is their performance to specification over time in response to varied, but specified, environmental stress conditions. Hitherto, advanced manufacturing techniques have continued to maintain FPGA reliability at a level that

is suitable for a large majority of applications. The semiconductor industry, based on ITRS, contemplates that the trade-off needs to remain at this level and continue to develop ICs with a failure rate of 50-2000 FITs (One Failure in Time equals to one failure in 10<sup>9</sup> hours) [7]. This means improving the reliability (in case of stochastic faults) of a transistor by a factor of five for technology nodes between 32 nm and 11 nm [8]. This may be a substantial challenge for a technology that is also faced with the manufacturing inadequacies in terms of process variation and yield complications.

The advanced techniques related to strained silicon and high- k gate dielectrics also pose considerable challenges for the suitable characterisation of device reliability. It, therefore, warrants implementation of innovative methods to realise continued scaling advantages and further enhance performance-efficiency. The deployment of multiple gates along with the new configurations of interconnect is one such example. However, the introduction of new materials and altering the structure of circuit components will result in substantial changes to the processes related to degradation. Ultimately, this may result in increased uncertainty about the reliability-performance relationship of devices.

FPGA reliability is envisaged to follow a downward trend, provided the existing thermal and power management mechanisms are optimised accordingly [9, 10, 11]. For instance, a considerable increase in the current density occurs with the decrease in the dimensions of the electron paths. This results in electromigration in interconnects - a particular concern. **Voltages**, though falling, are not matching the decrease in feature dimensions, thus generating high electric field strength - a dominant factor of acceleration in a number of degradation processes. Similarly, an increase in the threshold voltage is an indicator of FPGA ageing and the effect of this will enhance with shrunk supply voltage margins. Moreover, when it comes to the localised power dissipation, it is no different. The devices will experience increased levels of power dissipation due to higher circuit density. This may get compounded by a reduction in thermal conductivity, thereby causing higher junction temperatures (a key accelerating factor). In a nutshell, these wide-ranging challenges have the capacity to impact FPGA reliability in a number of ways. These could result in transient faults, such as the radiation-induced SEUs (Single Event Upsets), as well as performance degradation with transistor ageing [12].

#### 2.2.1 Degradation Mechanisms and Transistor Ageing

This subsection provides a concise overview of key degradation mechanisms that affect the reliability of FPGA in terms of CMOS transistors' ageing – a pressing reliability issue facing the VLSI devices at the nano-scale. The CMOS transistors are the underlying nano-architectures upon which the FPGA fabric is built. It is, therefore, prudent to investigate their performance, which ultimately helps adjudge FPGA health in terms of reliability.

Primarily, four degradation mechanisms are predominantly relevant to VLSI devices including FPGAs. These include: 1) Time-Dependent Dielectric Breakdown (TDDB), 2) Hot Carrier Injection (HCI), 3) Bias Temperature Instability (BTI), 4) and Electromigration (EM). In addition to these, the latch-up and soft-error generation are significant with respect to the environmental impact on the devices. These mechanisms are illustrated in Figure 2-6.

#### 2.2.1.1 Time Dependent Dielectric Breakdown (TDDB)

TDDB mechanism is the formation of a conductive path via the gate dielectric due to the accumulation of trapped charges, or defects. These trapped charges result due to the strong gate-bias voltage. As these defects weaken the dielectric at any explicit

Figure 2-6 The Degradation Mechanisms impacting the FPGA reliability [13].

location, a considerable amount of leakage current (I<sub>G</sub>) starts flowing with rapid increase in magnitude due to the reinforcement of the path [13].

#### 2.2.1.1.1 The Consequences

The consequential impact of TDDB is variable in nature due to the random variation of the breakdown path in conductivity and its physical location. When the breakdown condition is of mild nature, the increased leakage current results in increased power consumption and reduced switching speed. As the breakdown becomes severe in nature, higher power consumption is observed, which eventually prevents the transistor from switching, completely [14]. The main drivers of TDDB are the high temperature, thin oxide structures, and high electric fields and must be monitored for abnormalities.

#### 2.2.1.2 Hot Carrier Injection

This mechanism also known as the hot-carrier or hot-electron effect, is also based on defect accumulation process. However, it occurs in the interface region between the channel and the gate dielectric. The hot carriers in the channel with energies high enough to escape the potential barrier of the gate dielectric induce defects at the interface. When accelerated by the gate field, a series of collisions take place with the ions present in the interface region. This generates defects, which in turn, lead to an increase in threshold voltage and a decrease in the drain current or carrier mobility, resultantly slowing down the transistor switching [15]. This mechanism is particularly dynamic in CMOS, meaning it occurs when the transistors switch. The main factors that aggravate HCI are the high carrier velocities and shorter channel length.

#### 2.2.1.3 Bias Temperature Instability (BTI)