#### CRANFIELD UNIVERSITY

#### MAULANA RANDA

# DESIGN OF HARDWARE-ORIENTED SECURITY TOWARDS TRUSTED ELECTRONICS

# SCHOOL OF AEROSPACE, TRANSPORT, AND MANUFACTURING

Doctor of Philosophy Academic Year: 2017 - 2020

Supervisor: Prof. Ian K Jennions Associate Supervisor: Dr. Mohammad Samie July 2020

#### CRANFIELD UNIVERSITY

# SCHOOL OF AEROSPACE, TRANSPORT, AND MANUFACTURING

**Doctor of Philosophy**

Academic Year 2017 - 2020

#### MAULANA RANDA

Design of Hardware-oriented Security Towards Trusted Electronics

Supervisor: Prof. Ian K Jennions Associate Supervisor: Dr. Mohammad Samie July 2020

This thesis is submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy

© Cranfield University 2020. All rights reserved. No part of this publication may be reproduced without the written permission of the copyright owner.

#### **ABSTRACT**

While the Internet of Things (IoT) becomes one of the critical components in the cyber-physical system of industry 4.0, its root of trust still lacks consideration. The purpose of this thesis was to increase the root of trust in electronic devices by enhance the reliability, testability, and security of the bottom layer of the IoT system, which is the Very Large-Scale Integration (VLSI) device. This was achieved by implement a new class of security primitive to secure the IJTAG network as an access point for testing and programming. The proposed security primitive expands the properties of a Physically Unclonable Function (PUF) to generate two different responses from a single challenge. The development of such feature was done using the ring counter circuit as the source of randomness of the PUF to increase the efficiency of the proposed PUF. The efficiency of the newly developed PUF was measured by comparing its properties with the properties of a legacy PUF. The randomness test done for the PUF shows that it has a limitation when implemented in sub-nm devices. However, when it was implemented in current 28nm silicon technology, it increases the sensitivity of the PUF as a sensor to detect malicious modification to the FPGA configuration file. Moreover, the efficiency of the developed bimodal PUF increases by 20.4% compared to the legacy PUF. This shows that the proposed security primitive proves to be more dependable and trustworthy than the previously proposed approach.

#### Keywords:

Hardware Security, Physically Unclonable Function, Random Number Generator, JTAG, IJTAG, FPGA

### **ACKNOWLEDGEMENTS**

I would like to thank all those who have supported me in accomplishing this thesis. Without their endorsement, this thesis would not have been possible.

Foremost, I would like to pay my special regards to Dr. Anne Kusmayati for her encouragement for me to undertake a PhD and for the financial support I received through the Research and Development Agency of The Ministry of Defense of the Republic of Indonesia.

I would like to express the deepest gratitude to my supervisor, Professor Ian Jennions, for giving me the opportunity to work in Integrated Vehicle Health Management (IVHM) Centre and encouraging me to have the freedom to develop my ideas. These chances, together with his guidance, have helped to lead me through the process.

I am also deeply indebted to Dr. Mohammad Samie, my associate supervisor, who was also with me along this journey. His enthusiasm, constructive criticism, and fruitful discussions without which this thesis would be sorely diminished are most kindly acknowledged.

I wish to thank my wife and children for their support and patience over the course of my study period

Finally, I dedicate this work to my mother and father.

# **TABLE OF CONTENTS**

| ABSTRACT                                        | i    |

|-------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                | ii   |

| LIST OF FIGURES                                 | vi   |

| LIST OF TABLES                                  | viii |

| LIST OF EQUATIONS                               | ix   |

| LIST OF ABBREVIATIONS                           | x    |

| 1 INTRODUCTION                                  | 1    |

| 1.1 Background                                  | 1    |

| 1.2 Research Gaps/Industrial Needs:             | 3    |

| 1.3 Research Aim and Objectives                 | 5    |

| 1.3.1 Problem Description                       | 5    |

| 1.3.2 Hypothesis                                | 6    |

| 1.3.3 Aim                                       | 7    |

| 1.3.4 Objectives                                | 7    |

| 1.4 Research Methodology                        | 7    |

| 1.4.1 Research limitation                       |      |

| 1.5 The organisation of the thesis              |      |

| 1.6 Risk and mitigation plan                    | 12   |

| 1.6.1 Hardware description language             |      |

| 1.6.2 Modified IJTAG integration                |      |

| 1.6.3 Randomness measurement                    |      |

| 1.7 List of Published/Submitted Work            |      |

| 1.7.1 Journal Publications                      | 13   |

| 1.7.2 Conference Publications                   | 13   |

| 1.7.3 Virtual Conference Presentations          |      |

| 1.7.4 Under Submission for Journal Publication  |      |

| 1.8 References                                  |      |

| 2 DELAY-BASED TRUE RANDOM NUMBER GENERATOR IN S |      |

| NANOMILLIMETER IOT DEVICES                      |      |

| 2.1 Abstract                                    |      |

| 2.2 Introduction                                |      |

| 2.3 Related Works                               |      |

| 2.3.1 Random Number Generator                   |      |

| 2.3.2 Random Number Generator in FPGA           |      |

| 2.3.3 Test for Randomness                       |      |

| 2.3.4 Metrics                                   |      |

| 2.4 Experimentation                             |      |

| 2.4.1 Design of Ring Counter RNG (RCRNG)        |      |

| 2.4.2 Experimental Limitation                   |      |

| 2.5 Findings and Analysis                       | 31   |

|    | 2.6 Conclusion                                        | 38               |

|----|-------------------------------------------------------|------------------|

|    | 2.7 References                                        | 39               |

| 3  | A HIGH-SENSITIVITY SENSOR FOR THE DETECTION OF        |                  |

| 1U | NAUTHORISED MODIFICATIONS OF FPGA CONFIGURATION BASED |                  |

| 10 | N A PHYSICALLY UNCLONABLE FUNCTION                    | 43               |

|    | 3.1 Abstract                                          | 43               |

|    | 3.2 Introduction                                      | 43               |

|    | 3.3 Related Works                                     | 48               |

|    | 3.3.1 Physically unclonable function                  | 48               |

|    | 3.3.2 PUF characterisation                            | 51               |

|    | 3.4 Proposed works                                    | 52               |

|    | 3.4.1 Ring PUF as a digital sensor                    | 52               |

|    | 3.4.2 Uniqueness                                      | 55               |

|    | 3.4.3 Average reliability                             | 55               |

|    | 3.5 Experimental setup                                | 56               |

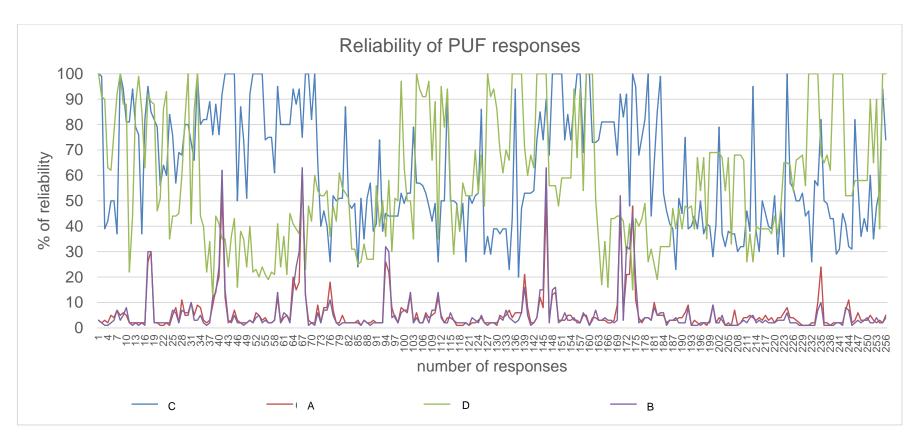

|    | 3.6 Findings and discussion                           | 60               |

|    | 3.6.1 RCPUF characterisation                          |                  |

|    | 3.6.2 RCPUF implementation as a sensor                | 63               |

|    | 3.6.3 Resistance to physical tampering and ageing     |                  |

|    | 3.7 Conclusion                                        | 67               |

|    | 3.8 References                                        | 67               |

| 4  |                                                       |                  |

| Pŀ | HYSICALLY UNCLONABLE FUNCTION                         | 73               |

|    | 4.1 Abstract                                          | 73               |

|    | 4.2 Introduction                                      |                  |

|    | 4.3 Related Works                                     | 78               |

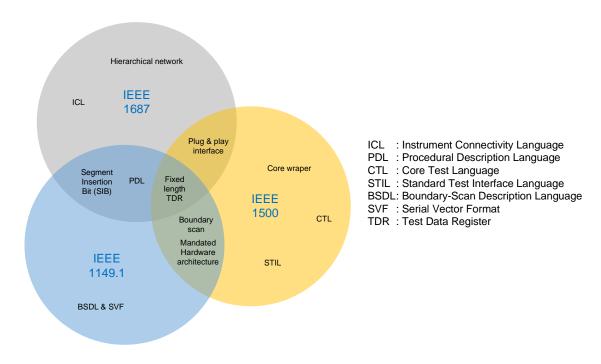

|    | 4.3.1 IEEE 1687 (IJTAG)                               | 78               |

|    | 4.3.2 Physically Unclonable Function (PUF)            | 81               |

|    | 4.3.3 PUF Metrics                                     | 83               |

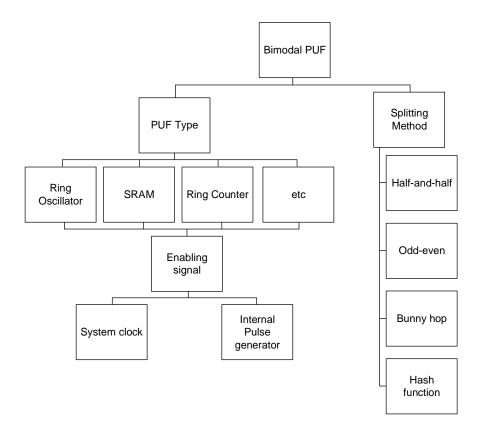

|    | 4.3.4 Splittable random number generator              | 84               |

|    | 4.4 Proposed Works                                    | 85               |

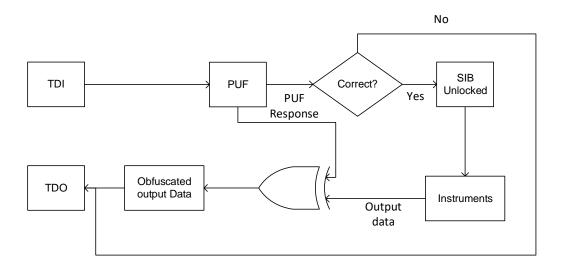

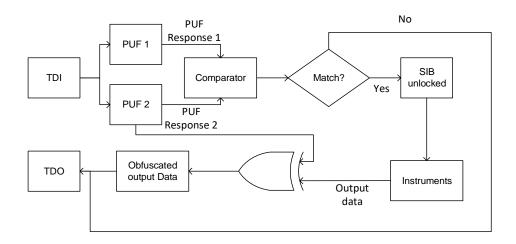

|    | 4.4.1 IJTAG Security Mechanism                        |                  |

|    | 4.4.2 Cost benefit analysis                           |                  |

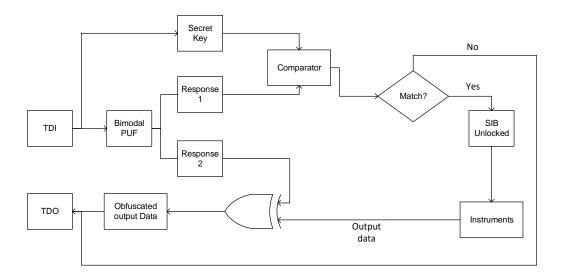

|    | 4.4.3 Bimodal PUF                                     | 92               |

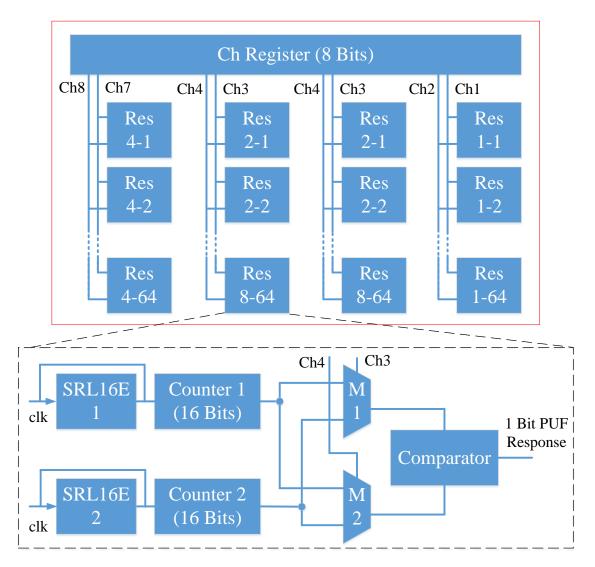

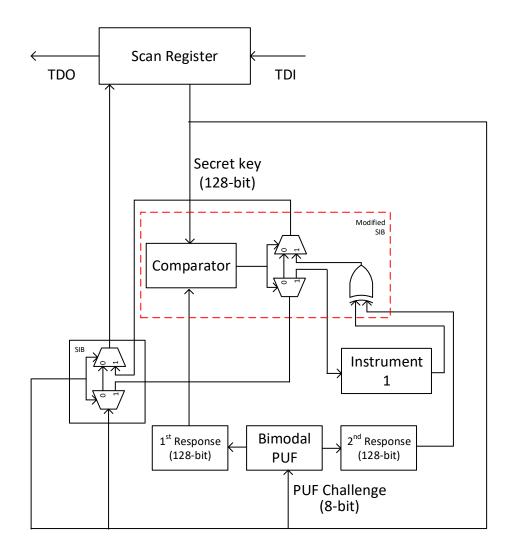

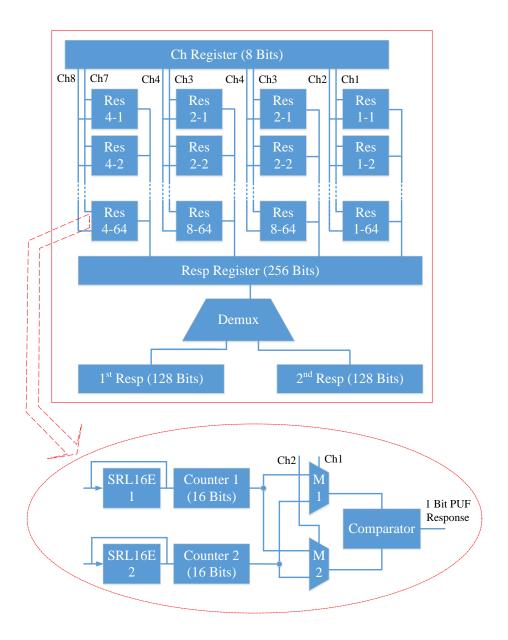

|    | 4.4.4 Design and architecture of the bimodal PUF      | 94               |

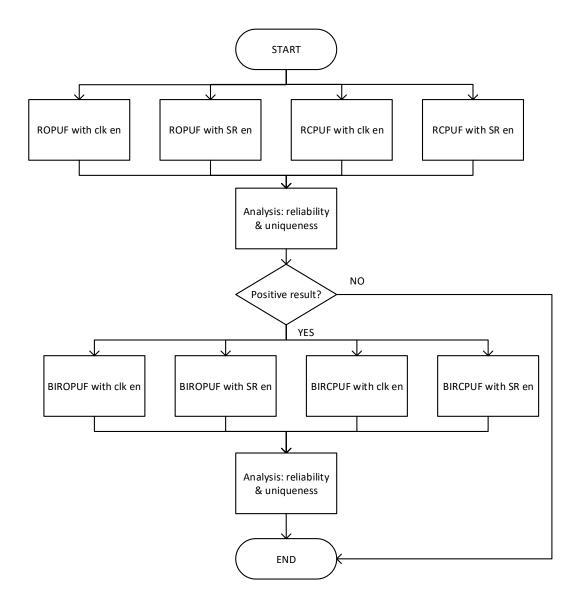

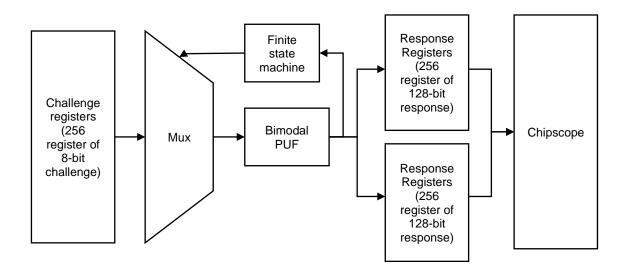

|    | 4.4.5 Experimental Setup                              | 98               |

|    |                                                       | ~ ~              |

|    | 4.5 Findings and Discussions                          | 99               |

|    | 4.5 Findings and Discussions                          |                  |

|    |                                                       | 99               |

|    | 4.5.1 Bimodal PUF Characterisation                    | 99<br>105        |

|    | 4.5.1 Bimodal PUF Characterisation                    | 99<br>105<br>107 |

| 111       |

|-----------|

| 112       |

| 113       |

| Design    |

| 113       |

| 114       |

| 115       |

| generator |

| 115       |

| generator |

| 117       |

|           |

# **LIST OF FIGURES**

| Figure 1-1: Hierarchy of security                                                                          | 1    |

|------------------------------------------------------------------------------------------------------------|------|

| Figure 1-2: Flowchart of the research                                                                      | 8    |

| Figure 2-1: RNG configuration (a) TRNG and (b) PRNG                                                        | . 20 |

| Figure 2-2: Block diagram of TRNG implementation                                                           | . 22 |

| Figure 2-3: Block diagram of TRNG implementation                                                           | . 28 |

| Figure 2-4: Location selection flowchart                                                                   | . 30 |

| Figure 2-5: Uniformity of the RC pairs on the first run                                                    | . 32 |

| Figure 2-6: Uniformity of the RC pairs on the second run                                                   | . 32 |

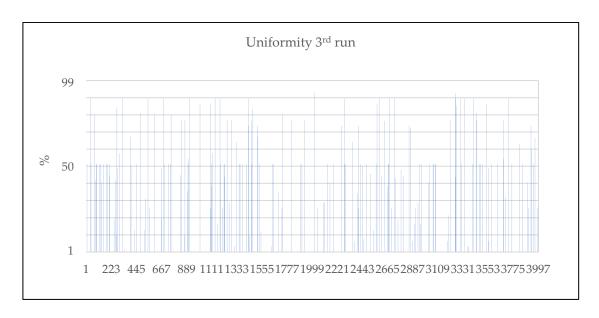

| Figure 2-7: Uniformity of the RC pairs on the third run                                                    | . 33 |

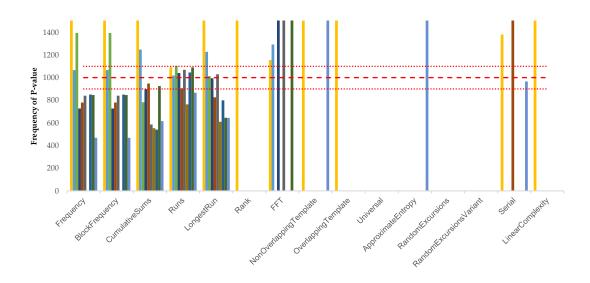

| Figure 2-8: Graphical presentation of the NIST test result                                                 | . 35 |

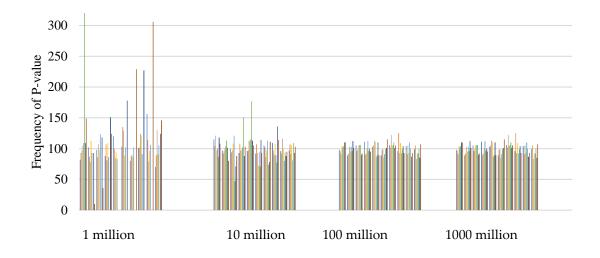

| Figure 2-9: Comparison of the different input bit lengths in the NIST test                                 | . 36 |

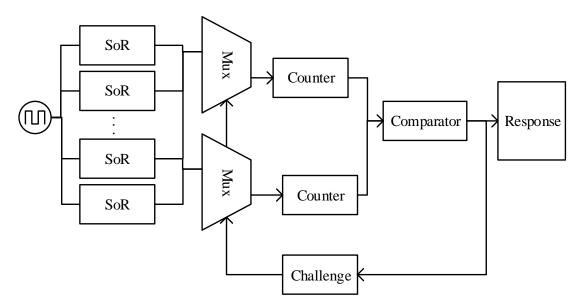

| Figure 3-1: Block diagram of a random number generator                                                     | . 48 |

| Figure 3-2: High-level schematic of delay-based PUF implementation                                         | . 49 |

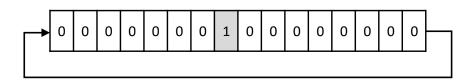

| Figure 3-3: Initialisation of the ring counter                                                             | . 53 |

| Figure 3-4: Block diagram of RC-based PUF                                                                  | . 54 |

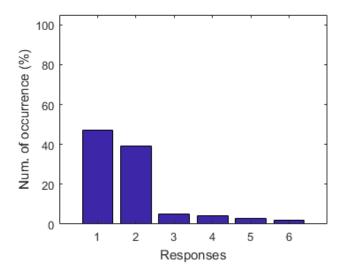

| Figure 3-5: Response variance from a single challenge                                                      | . 56 |

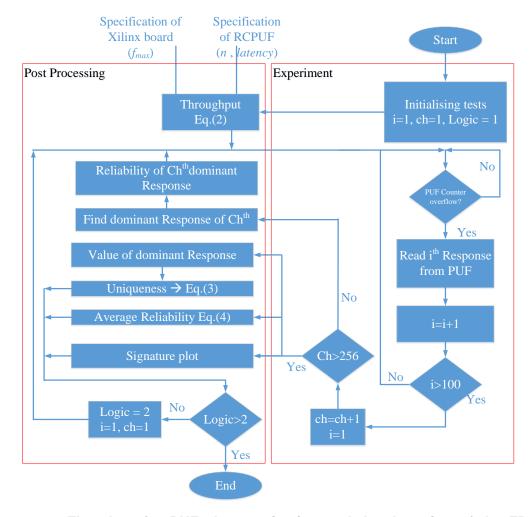

| Figure 3-6: Flowchart for PUF characterisation and the detection of the FP configuration file modification |      |

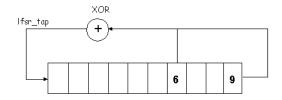

| Figure 3-7: LFSR setup                                                                                     | . 58 |

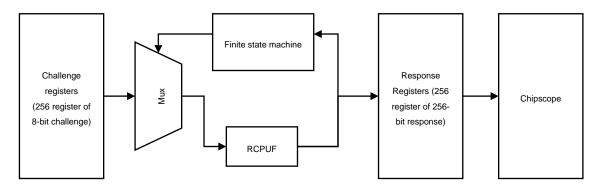

| Figure 3-8: Data acquisition setup                                                                         | 60   |

| Figure 3-9: Comparison of the reliability of the PUF responses                                             | . 64 |

| Figure 4-1: IEEE 1149.1 vs IEEE 1500 vs IEEE 1687                                                          | . 74 |

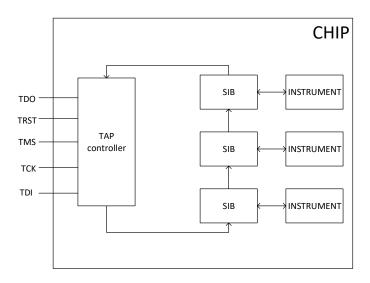

| Figure 4-2: IJTAG network with SIB and 3 Instruments                                                       | . 75 |

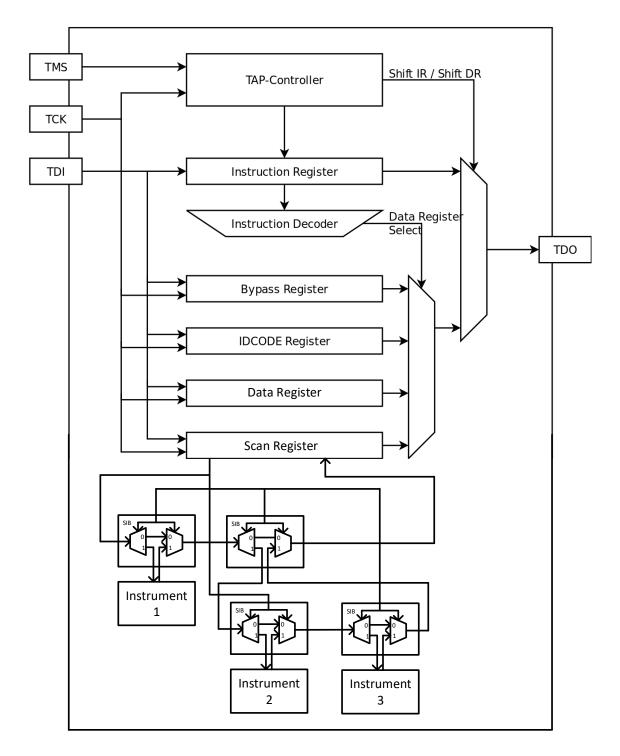

| Figure 4-3: IJTAG hierarchical network with a SIB                                                          | . 79 |

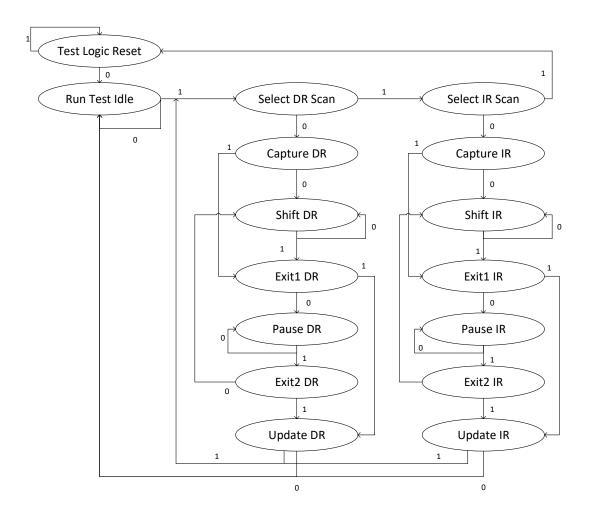

| Figure 4-4: State diagram of the TAP controller                                                            | . 80 |

| Figure 4-5: Flowchart of the IJTAG security with a reusable PUF response                                   | . 85 |

| Figure 4-6: Flowchart of the IJTAG security with 2 PUF implementations                                     | . 86 |

| Figure 4-7: Flowchart of the IJTAG security with the bimodal PUF                                           | . 87 |

| Figure 4-8: Multi-Layer security mechanism for the IJTAG network using bimodal PUF                                         |      |

|----------------------------------------------------------------------------------------------------------------------------|------|

| Figure 4-9: Classification of bimodal PUF                                                                                  | . 94 |

| Figure 4-10: RC-based bimodal PUF                                                                                          | . 96 |

| Figure 4-11: Experiment flow chart                                                                                         | . 98 |

| Figure 4-12: Data acquisition setup                                                                                        | . 99 |

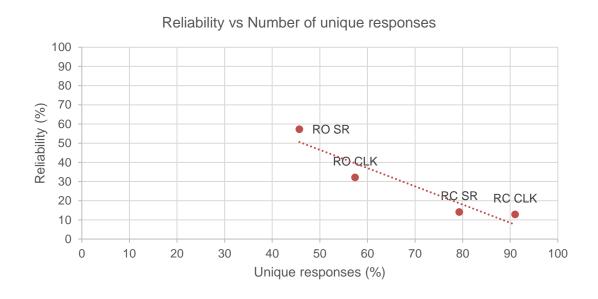

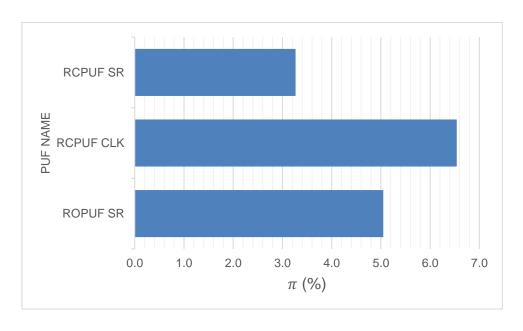

| Figure 4-13: Reliability VS Number of unique responses in the regular PUF.                                                 | 100  |

| Figure 4-14: Efficiency of the new PUF designs compared to the legacy F (ROPUF with a system clock as its enabling signal) |      |

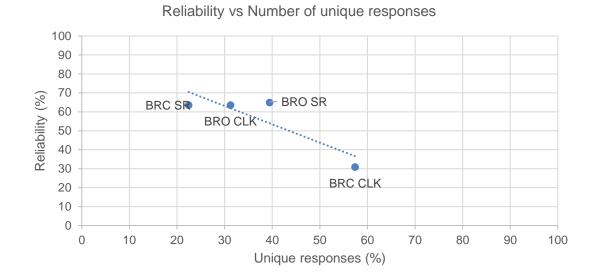

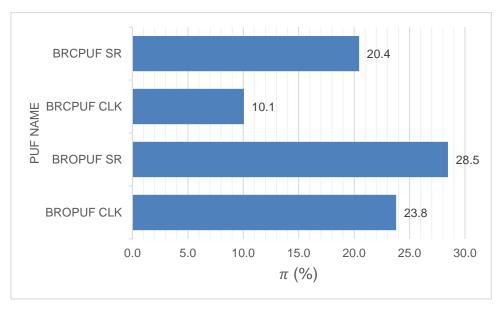

| Figure 4-15: Reliability VS Number of unique responses from the bimodal F                                                  |      |

| Figure 4-16: Efficiency of the bimodal PUF designs compared to the leg                                                     | •    |

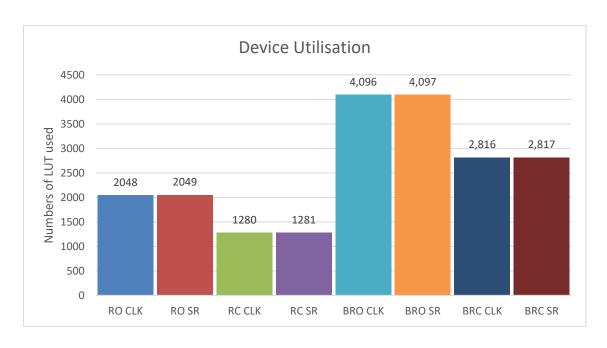

| Figure 4-17: Comparison of device utilisation                                                                              | 105  |

# **LIST OF TABLES**

| Table 2-1: Comparison Between TRNG and PRNG                                           |

|---------------------------------------------------------------------------------------|

| Table 2-2: Minimum Input for Different RNG Test Suites                                |

| Table 2-3: Statistical Tests Within NIST SP 800-2225                                  |

| Table 2-4: NIST SP 800-22 Test Results                                                |

| Table 2-5: NIST test results with 10 million input bits                               |

| Table 2-6: Throughput comparison between the TRNG implementation in FPGA              |

| Table 3-1: Various types of PUF50                                                     |

| Table 3-2: Pseudo code for the RCPUF mechanism                                        |

| Table 3-3: Experimental setup59                                                       |

| Table 3-4: Reliability and uniqueness comparison of RCPUF61                           |

| Table 3-5: Maximum working frequency and throughput62                                 |

| Table 3-6: Throughput comparison                                                      |

| Table 4-1: Splitting method for the splittable RNG                                    |

| Table 4-2: Assumption comparison for the secret key and PUF challenge confidentiality |

| Table 4-3: Pseudo-code for the RCPUF mechanism                                        |

| Table 4-4: Efficiency of the new PUF design compared to the legacy PUF 101            |

| Table 4-5: Efficiency of the bimodal PUF design compared to the legacy PUF            |

| Table 4-6: Comparison of the proposed method with other IJTAG security measures       |

# **LIST OF EQUATIONS**

| (2-1)  | 19 |

|--------|----|

| (2-2)  | 20 |

| (2-3)  | 26 |

| (3-1)  | 55 |

| (3-2)  | 56 |

| (4-1)  | 81 |

| (4-2)  | 81 |

| (4-3)  | 81 |

| (4-4)  | 90 |

| (4-5)  | 90 |

| (4-6)  | 90 |

| (4-7)  | 90 |

| (4-8)  | 91 |

| (4-9)  | 91 |

| (4-10) | 91 |

| (4-11) | 92 |

| (4-12) | 92 |

| (4-13) | 92 |

| (4-14) | 92 |

| (4-15) | 93 |

| (4-16) | 94 |

# **LIST OF ABBREVIATIONS**

| PUF    | Physically Unclonable Function                                              |

|--------|-----------------------------------------------------------------------------|

| SoR    | Source of Randomness                                                        |

| IoT    | Internet of Things                                                          |

| SR     | Shift Register                                                              |

| RC     | Ring Counter                                                                |

| RO     | Ring Oscillator                                                             |

| EDA    | Electronic Design Automation                                                |

| DRC    | Design Rule Check                                                           |

| CPS    | Cyber-Physical System                                                       |

| IP     | Intellectual Properties                                                     |

| RoT    | Root of Trust                                                               |

| ECT    | Embedded Core Test                                                          |

| JTAG   | Joint Test Access Group                                                     |

| IJTAG  | Internal JTAG                                                               |

| TRNG   | True Random Number Generator                                                |

| PRNG   | Pseudo-Random Number Generator                                              |

| RNG    | Random Number Generator                                                     |

| VLSI   | Very Large-Scale Integration                                                |

| RCRNG  | Ring Counter-based Random Number Generator                                  |

| RCPUF  | Ring Counter-based Physically Unclonable Function                           |

| ROPUF  | Ring Oscillator-based Physically Unclonable Function                        |

| BRCPUF | Bimodal Ring Counter-based Physically Unclonable Function                   |

| BROPUF | Bimodal Ring Oscillator-based Physically Unclonable Function                |

| nm     | nano millimetre                                                             |

| CRP    | Challenge-Response Pair                                                     |

| HDL    | Hardware Description Language                                               |

| VHDL   | VHSIC-HDL, Very High-Speed Integrated Circuit Hardware Description Language |

| NTV    | Near-Threshold Voltage                                                      |

| LUT    | Look-Up Table                                                               |

| FPGA   | Field Programmable Gate Array                                               |

| FIPS | Federal Information Processing Standard            |

|------|----------------------------------------------------|

| NIST | National Institute of Standard and Technology      |

| AIS  | Application Notes and Interpretation of the Scheme |

| PAR  | Placement and Route                                |

| VM   | Virtual Machine                                    |

| IC   | Integrated Circuit                                 |

| ID   | Identity                                           |

| TERO | Transient Effect Ring Oscillator                   |

| ASIC | Application Specific Integrated Circuit            |

| SRAM | Static Random-Access Memory                        |

| LFSR | Linear Feedback Shift Register                     |

| BIST | Built-in Self-Test                                 |

| TAP  | Test Access Port                                   |

| IUT  | Instrument Under Test                              |

| SIB  | Segment Insertion Bit                              |

| TDR  | Test Data Register                                 |

| TDI  | Test Data In                                       |

| TDO  | Test Data Out                                      |

| TMS  | Test Mode Select                                   |

| TRST | Test Reset                                         |

| TCK  | Test Clock                                         |

| FSM  | Finite State Machine                               |

#### 1 INTRODUCTION

## 1.1 Background

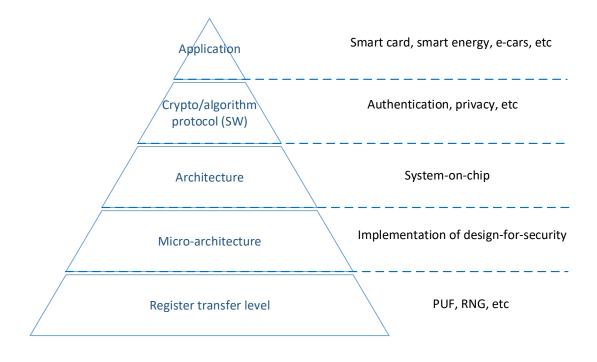

One of the moving components of industry 4.0 is the presence of a Cyber-Physical System (CPS). It is defined as a networked-embedded system that interacts with the environment [1], such as through autonomous vehicles or an industrial control system. The core of the CPS is the Internet of Things (IoT), which acts as an interface between the physical world and the cyber system. While bringing in many advantages, the IoT also brings in a couple of challenges, such as the security of the system. For an IoT device that has no area, time, power, and energy restriction (such as in a manufacturing plant), the security of the system can be easily implemented. However, for smaller IoT devices such as medical implants, where all of the parameters are constrained, the application of security measures needs to be well-thought-out. As suggested by Verbauwhede [2], the security of the system needs to be present in every different level of the system as a whole, as can be seen in Figure 1-1.

Figure 1-1: Hierarchy of security

A system or component needs to be trusted in order for it to run as expected for its intended purpose. In the old days, the threat to a system was more apparent in the communication channel between the nodes. One of the popular solutions to such an old-style threat is to protect the data through the implementation of a strong cryptographic protocol. However, the threat model for a modern system not only comes into play in the communication channel itself but also the nodes. When the component that provides the cryptographic protocol is not secure, the service that it provides is also threatened. Therefore, a Root of Trust (RoT) needs to be built into a system. Referring to Figure 1-1, Verbauwhede [2] defines the RoT of a system as a measure to account for the trustworthiness of the systems located in the lower-level layers. The extreme end of this definition means that in order to have a secure system, the lowest layer of the system, the transistor level, needs to be secure too.

The ever-evolving world of semiconductors has led to more complex Very Large-Scale Integration (VLSI) devices in terms of structure and functionality. While this advancement provides an advantage as there is more of a possibility of solving different kinds of problems, it also becomes a problem in itself. The increase in functional complexity means that more things can go wrong if it is not well-designed. For example, a different type of confidential information stored in IoT devices can be compromised if there is not enough protection. A Cloud-computing service with shared resources can become an easy target for intellectual property thievery [3]. The complexity of providing a secure environment for this kind of technology is enhanced by the fact that it is getting harder to perform affordable and fast testing procedures before the product is deployed in the market. It is almost impossible to physically probe all pins in the VLSI device to test its functionality.

The IEEE 1149.1 JTAG, IEEE 1500 Embedded Core Test (ECT), and IEEE 1687 Internal JTAG (IJTAG) have become the standard tests used to overcome the aforementioned testing challenges. The three standards have their own specificities and were made to be used side by side.

Other than the favourable circumstances that it brings in to the testability of the embedded instruments, JTAG confronts various security-related difficulties when it is utilised as the future standard of embedded instrument testing. The first is that the JTAG does not have a built-in security mechanism to forestall unauthorised access to the embedded instrument. A report about security breaks by means of JTAG can be found in the news [4] and papers [5]. Majeric [6] and Elnaggar [7] presented the JTAG fault injection attack and data integrity attack consecutively to modify the Intellectual Property (IP) core maliciously, steal classified information, reverse engineer the IP, and even stop the entire framework if it is undermined. Hence the security of the IJTAG network that gives access to the gadget is essential.

While it is also of importance to secure the embedded core, it is still a challenge to provide security to the ECT standard. The reason for this is that the ECT standard is prescriptive, which means that a modification to the standard will break the compliance of the system to the standard. On the other hand, the IJTAG standard is descriptive, which means that the engineer can have different implementations of the standard so long as they follow the description of the standard. Hence the security of the IJTAG will be the main topic of discussion in this thesis.

There is ongoing research into providing better security in IJTAG networks such as the use of a static secret key ([8], [9]) and dynamic secret key ([10], [11]) to unlock the Segment Insertion Bit (SIB). However, they only secure access to the IJTAG network without securing the output data from the embedded instrument. An echeloned IJTAG data protection mechanism [12] that is proposed to secure the access, as well as the output data, is also facing a scalability problem.

# 1.2 Research Gaps/Industrial Needs:

Having noticed the challenges, it is identified that building the security and root of trust into electronics is a critical industrial requirements for the future embedded systems. It is a need now to develop novel security mechanisms for devices'

access ports; especially, the widely used IJTAG network additional to the conventional approach of data security using some form of cryptography. From a hardware implementation point of view, building the security in the embedded systems requires characterisation of embedded devices based on their performance variations raised from physical changes and manufacturing process. This is usually conducted by observing physical resources, which expose the hardware in various performance variations; and employing it to develop electronic signatures, device identification, and digital fingerprint. This; obviously, involves various fields in design, test, and manufacturing of electronics, while each has specific gaps; however, we limit the research to address the following observed challenges:

#### Gaps in the hardware root of trust

The bottom layer of the root of trust lies within the transistor level of the device. However, the current access port and test mechanisms are primarily developed without any consideration of the root of trust. Therefore, it is of importance to secure access to the test mechanism as well as securing its data to achieve better security.

#### • Gaps in observing the source of randomness in the hardware level

The emergence of sub-nano millimetre electronic device needs to be well secured against adversaries. However, the current security measures are only available in the form of algorithmically generated a random number, which can be broken easily using deep learning. Thus, a true random number generator based on the physical variation of the device needs to be developed and characterised to understand its performance in sub-nm technology.

#### Gaps in the device identification

One of the critical aspects of security is to be able to identify whether a device is an original, counterfeited or modified part. A security primitive that can be used for such purpose is the Physically Unclonable Function (PUF). However, the current mechanism for device identification using PUF relies on the response of the PUF, which easily altered by

environmental change. Thus, it is of importance to develop a new mechanism that has better resistance to environmental change.

#### Gaps in performance analysis

The performance analysis of a PUF is done by comparing the response variance of a PUF architecture implemented in two or more devices exposed to environmental variation. This mechanism requires the device to be in a test mode, which increases the down time of the system. However, it is always a desire to lower the down time. Thus, it is of importance to develop a new PUF performance analysis mechanism that can be performed in mission mode; and hence, decreasing the down time.

## 1.3 Research Aim and Objectives

#### 1.3.1 Problem Description

Given embedded electronics as a collection of primitive components, circuitries, building blocks in the form of IPs fabricated as ASIC/FPGAs/SoCs; there are still technical problems for exploiting the device's performance variation in the development of root of trust. Such devices are equipped with test access ports, networks, and mechanisms, which allow external device-to-device and internal instrument-to-instrument communications needed for testing the function of specific hardware entities within the device. They are not intended for testing the performance of the device needed to assess the system concerning the security. Therefore, existing advanced test mechanisms do not have the capability for observing sources of randomness induced to the system unintentionally due to manufacturing process variation. Such variations are monitored using parameters such as power consumption, temperature, and propagation delays for the same particular devices against the specific working condition. Monitoring such signals requires enhancing internal test network with a proper sensor network distributed across the entire device. As only a few sensors are fabricated into the embedded electronics, designers would need to employ available resources and primitives to form sensors for observing the sign of variation from

device to device. This leaves us with the following problems for building root of trust:

Given embedded electronics with n number of sensors built using m primitives distributed across the entire system, device performance variation is observed in the form of propagation delays which drive electronic fingerprint, specific for a particular device under test, different from all other similar prototypes. The generated fingerprint is the key element needed for controlling access to the hardware as well as the encryption of the data generated by the hardware. This requires additional care in:

- Identifying proper signals linked with sources of randomness in the device

- Architecting right set of sensors using available primitives fabricated within the device

- Generating fingerprints from signals observed from the source of the randomness

- Integrating sensor network and the required signal path with the test access mechanism

- Building the root of trust

The conventional design flow does not yet allow engineers to construct the device identity and the root of trust, which is essential for the protection of vulnerabilities in ASICs, FPGAs and SoCs. In response to the problem mentioned earlier, this dissertation explores the accessibility of the conventional test access mechanism to break the bottleneck of the development of security and trust in embedded electronics.

### 1.3.2 Hypothesis

Building bimodal characteristics into the performance of the physically unclonable function (which drives electronic fingerprint from the source of randomness observed by the random number generators) enables designers to construct a

unique solution for obfuscating both the hardware and data, which lead to the establishment of the root of trust essential for the test access mechanisms. In this regard, the customizability of the security primitives within the test access allows for the exploration of the devices' source of randomness to secure the access and information of the IPs within the embedded electronics.

#### 1.3.3 Aim

In order to address the aforementioned research gaps, this thesis aims to improve the security of the embedded system through the development and implementation of design-for-security.

### 1.3.4 Objectives

Based on the aim of the research above, the following key objectives have been defined to achieve the aim:

- 1. Develop and characterise a novel random number generator design based on the ring counter circuit (RCRNG).

- 2. Develop and characterise a novel digital physically unclonable function based on the ring counter circuit (RCPUF).

- To develop and characterise bimodal RCPUF (BRCPUF) to secure access to the IJTAG network as well as its output data.

# 1.4 Research Methodology

In response to the gaps mentioned earlier, we propose a novel security mechanism developed based on a Physically Unclonable Function (PUF), which is a product of the utilisation of the physical randomness of an object/device that is easy to produce, but non-invertable and unpredictable [13]. A PUF can also be defined as a constrained True Random Number Generator (TRNG). Therefore, an understanding of TRNG is a fundamental requirement to develop a PUF.

Build upon the requirement as mentioned above; this thesis will first discuss the development of a true random number generator. The findings and experience drawn from the development of a TRNG will be used to develop a PUF which will then be used to develop the bimodal PUF to secure the IJTAG network.

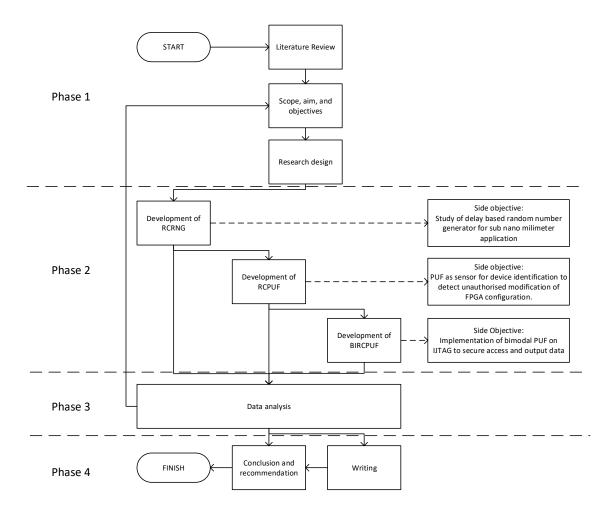

The research methodology is divided into 4 phases, as illustrated in Figure 1-2. The first phase is where the gaps in the field of research are discovered by performing an extensive literature review. The scope of the research is then defined to focus on the area of study. From there on, the aim and objectives of the research are formalised. The research design is then developed as a guideline for the experiment to be performed in accordance with the aim and objectives of the research.

Figure 1-2: Flowchart of the research

The second phase is the experimental phase. The initial idea of this research is to find an efficient design-for-security element to secure an embedded system. For that matter, this research proposed a new class of Physically Unclonable Function (PUF) which will then be called a bimodal PUF. In order to develop a bimodal PUF, knowledge on how to develop a regular PUF is a prerequisite. Moreover, an understanding of the Random Number Generator (RNG) is needed to construct a PUF as it is the basic building block of PUF. Therefore 3 experiments are designed to achieve the aim and objectives of the research.

The first experiment is to develop a random number generator based on the Ring Counter (RC) circuit. Apart from getting an understanding of how the RNG works and behave, this experiment also aimed to implement the developed RNG as a model to study the characteristics of a delay-based RNG in sub-nano millimetre technology. The reason why this topic is chosen to be studied is that the behaviour of the TRNG as one of the critical components to provide security in sub-nano millimetre (nm) devices is not well-studied. It is essential to understand its characteristics when it is implemented in the sub-nm, so then the hardware security designer knows what to expect and can develop a better implementation of TRNG for security purposes in sub-nm devices.

After gaining a better understanding of the development of a TRNG, the second experiment is conducted to develop a PUF based on the ring counter circuit. As has already been mentioned above, the basic building block of a PUF is a random number generator. In a digital circuit, the PUF is created by selectively choosing an array for the Source of Randomness (SoR) comparison, so then the output is reproducible. A challenge in the form of a binary number is used to select which source of randomness is to be compared. The output of the PUF is then called the response. Each challenge will, ideally, generate a unique response. This can also be called a challenge-response pair (CRP). The source of randomness for the PUF is based on the ring counter circuit. Aside from characterising and gaining a better understanding of how the PUF works, this experiment also aimed to implement the developed PUF as an affordable high-sensitivity digital sensor

to detect unauthorised modifications to the configuration file of multi-tenant FPGA. This has now become an emerging trend in Cloud computing.

Lastly, the third experiment is conducted to develop a new class of physically unclonable functions called a bimodal PUF. It is aimed to be a design-for-security solution for embedded devices. The bimodal PUF is characterised and implemented in the IJTAG network to not only efficiently secure the access to the embedded instruments but also to secure the output data of the embedded instruments.

All three experiments have a common thread in that they all utilise the ring counter circuit as the main source of randomness. To the best of the author's knowledge, no publication uses a ring counter as the primary source of randomness in their research. Therefore, the utilisation of the ring counter circuit as the main source of randomness is claimed to be one of the novelties in this research. The other innovations in this research are as follows:

- 1. Study on the behaviour of a delay-based random number generator in subnano millimetre technology.

- 2. A novel high-sensitivity digital sensor to detect unauthorised modifications of the configuration file of a multi-tenant FPGA.

- 3. A new definition of the uniqueness and reliability parameters for PUF characterisation.

- 4. A new class of PUF that can generate two simultaneous responses from a single challenge. This new class of PUF will be called a bimodal PUF.

#### 1.4.1 Research limitation

The majority of publications about hardware security include a discussion on the performance of the proposed work under different environmental conditions. For example, silicon-based hardware security primitives are said to incur a behavioural change under different temperatures and/or supply voltage stress. The system may not behave as it is intended to be or may leak confidential information that the security primitives are trying to hide.

However, this thesis will not include such a test in the discussion part of each chapter. Nonetheless, it does not lower the confidence level of the obtained experimental result. The reason for this is that in order to perform such a measurement, the decapsulation process needs to be done to the chip-undertest [14]. All security primitives proposed in this thesis (TRNG, PUF, bimodal PUF) are implemented as on-chip security. This means that the security mechanism and the object have tried to secure what resides in the same chip. Consequently, when an attacker is trying to break the security measures by increasing the supply voltage or/and the temperature, and they conduct the measurement without the decapsulating process, they will not be able to get an accurate measurement, and therefore the obtained information will not be accurate. If the attacker performs the decapsulation procedure, it will change the physical properties of the security mechanism. Consequently, the response generated by the security mechanism will also change. Moreover, the temperature/voltage stress applied to the chip might even break the information that the attacker is trying to get as it operates beyond the specification given by the manufacturer.

## 1.5 The organisation of the thesis

The main content of the thesis is divided into three chapters in a paper format. What this means is that each chapter/paper will have a literature review, aim and objectives, research methodology and analysis. However, all three chapters/paper do not stand on their own. They are more of a stepping stone to the chapter following the previous one. Chapter 2 of this thesis discusses the development of a random number generator which will be used as a building block to build a PUF in Chapter 3. Similarly, the PUF developed in Chapter 3 will be used as the foundation to develop the bimodal PUF in Chapter 4. The last chapter of this thesis is the conclusion that serves as a retrospective examination of what has been done in relation to the aim and objectives of the thesis. Chapter 5 also discuss the possibility of future work that can be done as a further development of the things presented in this thesis.

### 1.6 Risk and mitigation plan

#### 1.6.1 Hardware description language

Hardware design involves the use of Hardware Description Language (HDL). There are three types of HDL; Verilog, System Verilog and VHDL (VHSIC-HDL and Very High-Speed Integrated Circuit Hardware Description Language). For this thesis, the author chooses to use the VHDL because it has non-C like syntax. This is easier to be used by people who do not have a strong background in programming. Nevertheless, the author needs some time to adapt to the VHDL as well as the complexity of the Electronic Design Automation (EDA) software used, e.g. ISE 14.7 from Xilinx.

The mitigation plan used to overcome this situation is to do the task manually, i.e. to hard-code the VHDL file. Nevertheless, this limitation did not reduce the confidence level of the results obtained in the experiment.

## 1.6.2 Modified IJTAG integration

The configurability of the IJTAG to include segment insertion bit is what separates it with the JTAG. The IJTAG network needs to be synthesised together along with other logic of the ASIC. However, because of the time and resource limitation, the ASIC implementation of the proposed IJTAG network cannot be done.

As a solution to this situation, the author implements the modified IJTAG network in FPGA. FPGA primitives and resources are used to model the IJTAG functionality and integrate the proposed PUF for the IJTAG security mechanism.

#### 1.6.3 Randomness measurement

The Statistical Test Suite for Random and Pseudorandom Number Generators for Cryptographic Applications NIST SP 800-22 [15] standard was used to measure the randomness of the RNG in this thesis. The standard consists of 15 statistical tests. The standard decides whether an RNG has the right amount of

randomness or not by thresholding the output of each of the statistical tests. Because of this, it is possible for an RNG that falls below the threshold by just a small amount to be considered to fail the test.

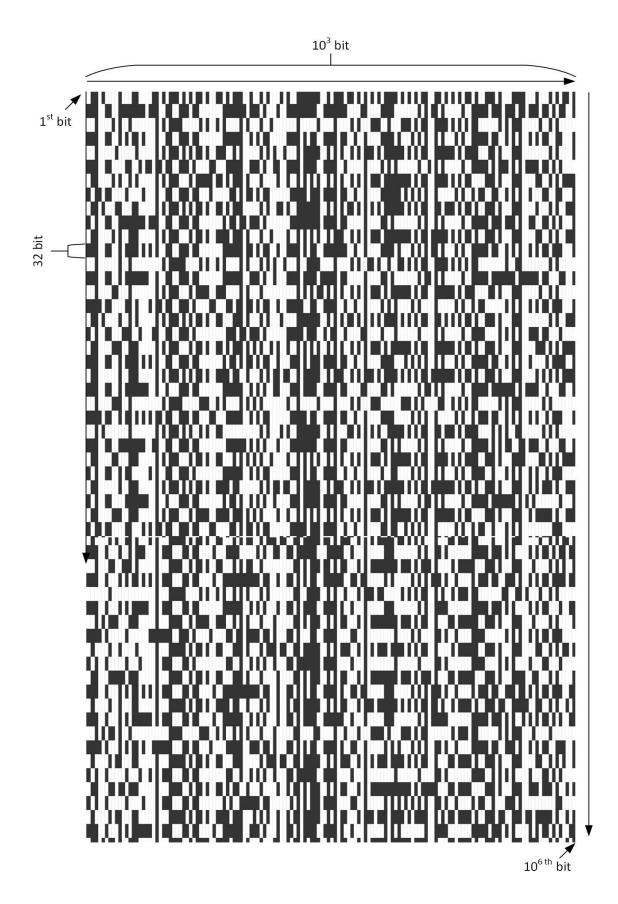

To overcome this situation, the NIST SP 800-22 suggests that the tester perform a graphical analysis to determine the high-level performance of the RNG undertest. The graphical analysis can be done by plotting the results of the statistical tests in a bar chart or by plotting the generated random number using a heat map.

#### 1.7 List of Published/Submitted Work

#### 1.7.1 Journal Publications

M. Randa, M. Samie, I. Jennions. "Delay-Based True Random Number Generator in Sub-Nanomillimeter IoT Devices," in *Electronics* 2020, *9*, 817.

#### 1.7.2 Conference Publications

M. Randa, M. Bozdal, M. Samie, I. Jennions. "Layered Security for IEEE 1687 Using a Bimodal Physically Unclonable Function," in *Procedia Manufacturing*. 2018; 16:24-30.

M. Bozdal, M. Randa, M. Samie, I. Jennions. "Hardware Trojan Enabled Denial of Service Attack on CAN Bus," in *Procedia Manufacturing*. 2018;16:47-52.

#### 1.7.3 Virtual Conference Presentations

J. Buu-Sao, M. Samie, M. Randa, et. al., "IoT Security – Hardware Perspective", December 2018, the IoT Day Slam 2018, VIRTUAL Internet of Things Conference: https://iotslam.com/session/iot-security-hardware-perspective/.

#### 1.7.4 Under Submission for Journal Publication

M. Randa, M. Samie, I. Jennions. "A High-Sensitivity Digital Sensor For The Detection of Unauthorised Modifications of Multi-Tenant FPGA Configuration Files Based On A Ring Counter Physically Unclonable Function,". – Under review for IEEE Access, July 2020

#### 1.8 References

- [1] G. Loukas, "A Cyber-Physical World," in *Cyber-Physical Attacks*, London: Elsevier, 2015, pp. 1–19.

- [2] I. Verbauwhede, "Hardware Security Knowledge Area," in *The Cyber Security Body Of Knowledge*, 1.0., Andrew Martin and G. Danezis, Eds. Bristol: University of Bristol, 2019.

- [3] J. Robertson and M. Riley, "The Big Hack: How China Used a Tiny Chip to Infiltrate U.S. Companies Bloomberg," *Bloomberg.com*, 2018. [Online]. Available: https://www.bloomberg.com/news/features/2018-10-04/the-big-hack-how-china-used-a-tiny-chip-to-infiltrate-america-s-top-companies. [Accessed: 02-Jun-2020].

- [4] R. Johnson, "Sergei Skorobogatov Defends Backdoor Claims Business Insider," *Business Insider*, 2012. [Online]. Available: https://www.businessinsider.com/sergei-skorobogatov-defends-backdoor-claims-2012-5?r=US&IR=T. [Accessed: 30-May-2020].

- [5] S. Skorobogatov and C. Woods, "Breakthrough silicon scanning discovers backdoor in military chip," *Lecture Notes in Computer Science (including subseries Lecture Notes in Artificial Intelligence and Lecture Notes in Bioinformatics)*, vol. 7428 LNCS, pp. 23–40, 2012.

- [6] F. Majéric, B. Gonzalvo, and L. Bossuet, "JTAG Fault Injection Attack," *IEEE Embedded Systems Letters*, vol. 10, no. 3, pp. 65–68, Sep. 2018.

- [7] R. Elnaggar, R. Karri, and K. Chakrabarty, "Securing IJTAG against data-

- integrity attacks," in *Proceedings of the IEEE VLSI Test Symposium*, 2018, vol. 2018-April, pp. 1–6.

- [8] J. Dworak, A. Crouch, J. Potter, A. Zygmontowicz, and M. Thornton, "Don't forget to lock your SIB: Hiding instruments using P16871," in *Proceedings* - *International Test Conference*, 2013, pp. 1–10.

- [9] H. Liu and V. D. Agrawal, "Securing IEEE 1687-2014 Standard Instrumentation Access by LFSR Key," in *Proceedings of the Asian Test Symposium*, 2015, vol. 2016-Febru, pp. 91–96.

- [10] R. Baranowski, M. A. Kochte, and H. J. Wunderlich, "Fine-grained access management in reconfigurable scan networks," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 34, no. 6, pp. 937–946, Jun. 2015.

- [11] K. Sudeendra Kumar, N. Satheesh, A. Mahapatra, S. Sahoo, and K. K. Mahapatra, "Securing IEEE 1687 standard on-chip instrumentation access using PUF," in *Proceedings 2016 IEEE International Symposium on Nanoelectronic and Information Systems, iNIS 2016*, 2017, pp. 56–61.

- [12] S. Kan, J. Dworak, and J. G. Dunham, "Echeloned IJTAG data protection," in *Proceedings of the 2016 IEEE Asian Hardware Oriented Security and Trust Symposium, AsianHOST 2016*, 2017, pp. 1–6.

- [13] S. Mulhem and W. Adi, "New Mathblocks-Based Feistel-Like Ciphers for Creating Clone-Resistant FPGA Devices," *Cryptography*, vol. 3, no. 4, p. 28, Dec. 2019.

- [14] M. Hutter and J. M. Schmidt, "The temperature side channel and heating fault attacks," in *Lecture Notes in Computer Science (including subseries Lecture Notes in Artificial Intelligence and Lecture Notes in Bioinformatics)*, 2014, vol. 8419 LNCS, pp. 219–235.

- [15] A. Rukhin *et al.*, "Special Publication 800-22 Revision 1a A Statistical Test Suite for Random and Pseudorandom Number Generators for Cryptographic Applications," Apr. 2010.

# 2 DELAY-BASED TRUE RANDOM NUMBER GENERATOR IN SUB-NANOMILLIMETER IOT DEVICES

#### 2.1 Abstract

True Random Number Generators (TRNGs) use physical phenomena as their source of randomness. In electronics, one of the most popular structures to build a TRNG is constructed based on the circuits that form propagation delays such as a ring oscillator, shift register, and routing paths. This type of TRNG has been well-researched within the current technology of electronics. However, in the future where electronics will use sub-nano millimetre (nm) technology, the components become smaller and work on near-threshold voltage (NTV). This condition has an effect on the timing-critical circuit as the distribution of the process variation becomes non-gaussian. Therefore, there is an urge to assess the behaviour of the current delay-based TRNG system in sub-nm technology. In this research, a model of TRNG implementation in sub-nm technology was created through the use of a specific Look-Up Table (LUT) in the Field-Programmable Gate Array (FPGA), known as SRL16E. The characterization of the TRNG was presented, and it shows a promising result, in that the delay-based TRNG will work properly with some constraints in sub-nm technology.

#### 2.2 Introduction

In the era of the internet of things (IoT), everyone feels the need for privacy and security because their private data is floating around in the connected cloud [1]. As IoT-based systems have both hardware and software requirements, there is always a potential for systems to be hacked if the hardware is not as well-secured to a suitable level as the software. Research in recent years has demonstrated the existence of malware that could be removed from the system if appropriate software-level countermeasures are set up, correctly [2]. Hackers might target such malware for hacking the physical systems. Therefore, hardware security is also an essential requirement, besides the security of the software, to ensure that

the security of the system and the privacy of the user's data are well-established [2].

Cryptography is now essential for securing access to both the data and hardware, which is necessary for IoT-based systems [3]. A key is a vital aspect for cryptography, and it can be created using a Random Number Generator (RNG). There are two types of random number generator; a true random number generator (TRNG) and a pseudo-random number generator (PRNG). The comparison between TRNG and PRNG has been summarized in Table 2-1.

Table 2-1: Comparison Between TRNG and PRNG

| TRNG                                                      |                                | PRNG                   |

|-----------------------------------------------------------|--------------------------------|------------------------|

| Source of randomness Physical phenomenon Mathematical alg |                                | Mathematical algorithm |

| Uniformity                                                | niformity Yes                  |                        |

| Independence                                              | ence Yes No (Periodic/determin |                        |

| Efficiency                                                | low                            | high                   |

While a pseudo-RNG (PRNG) is simple to implement and sufficient enough for many applications, there is always a desire to have a TRNG, especially for highly critical systems. The reason for this is that PRNG was created from a computational algorithm that has deterministic properties. When the algorithm behind the PRNG is compromised, the random number that it generates is also compromised. On the other hand, a TRNG utilizes a physical system that has intrinsic randomness, which can be extracted to create an RNG. This results in non-deterministic properties for the TRNG.

There have been various designs and technologies suggested for architecting TRNGs for different types of IoT. For a big-sized IoT, such as a smart-fridge, smart-toaster etc., a TRNG that uses optical scattering [4], [5] and radioactive decay [6] as its source of randomness (SoR) can be used. While these TRNGs are bulky and have low efficiency, they have an excellent randomness property. For smaller IoT devices such as a smartphone, the use of sensors such as an

accelerometer and gyroscope as the source of randomness have been reported to have excellent results [7]–[9]. However, the implementation of these approaches still relies on external data processing, e.g. a PC, which is impossible to include in resource-constrained devices such as an implanted IoT like a pacemaker. For this type of IoT, a TRNG that utilizes the intrinsic parameters of the devices is preferred as they do not have to rely on the external source of randomness.

An all-digital RNG implemented in 65nm and 14nm technology was proposed in [4] and [5] respectively. Pamula [4] proposes a high-quality RNG based on a processed low-quality RNG with intrinsic SoR. Their analysis shows excellent performance. However, the technology used is too big for an implanted IoT. In [5], the author implements TRNG in the latest semiconductor technology. However, the source of randomness used is not always available in the IoT devices, making it difficult to achieve in IoT. In modern FPGA technology, the SRL16E is standard, and it has the potential to be used in TRNG. The author in [9, 10] uses the SRL16E and configures it to be a ring counter in order for it to become one of the components of their TRNG. However, they only use the ring counter as a complementary component to increase the periodicity of the RNG and not as the primary source of randomness.

Moreover, the size of transistors in the future will become smaller beyond nanomillimetre technology [6]. This causes the electronic devices to run at a nearthreshold voltage (NTV) [7]. These phenomena have an impact on the critical timing of the device because the distribution of the process variation is nongaussian [8]. A couple of research studies have been done to address this issue [9], [12]. However, from the extensive literature review, a report on the effect of NTV in the time-critical application such as a delay-based random number generator is not in existence.

This chapter presents a study on the implementation of delay-based TRNG intending to explore TRNG performance and properties in sub-nm technology. The sub-nm delay-based RNG was modelled in FPGA using a ring counter based on the SRL16E configuration of Xilinx's LUT as the main source of randomness.

The rest of the chapter is organised as follows: Section 2.3 provides an introduction to RNG implementation in the FPGA and the metrics for RNG characterization. The experimental setup, practical limitations, and a framework for location selection are presented in section 2.4. The results, findings, and statistical analysis are discussed in Section 2.5. Finally, this chapter will be concluded in Section 2.6.

#### 2.3 Related Works

#### 2.3.1 Random Number Generator

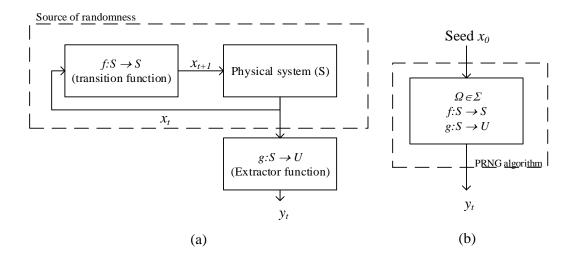

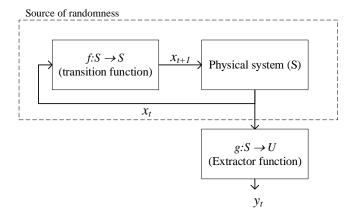

The idea of a random number generator is based on stochastic modelling in which an observable random variable can be obtained from a random phenomenon. In a random number generator, let S be the state space of the generator, which is also a subset of a set  $\Omega$ . The random variable generated is part of the random space U that is extracted using the extraction function g. What is being obtained by g is a mapped state space S by function f so that  $f:S \to S$ .

$$\Omega \in S$$

$$f: S \to S \tag{2-1}$$

$$g: S \to U$$

In a True Random Number Generator (TRNG), f is the physical source of randomness and g is the logic or function used to process the source of randomness further. In a Pseudo-Random Number Generator (PRNG), f and g are the mathematical algorithms used to generate the random number. Both TRNG and PRNG need an initial condition. In TRNG, the initial condition is any current state of the physical system while in PRNG, the initial condition needs to be provided by the seed  $x_0$ . Figure 2-1 is given to illustrate this mechanism.

Figure 2-1: RNG configuration (a) TRNG and (b) PRNG

In semiconductor devices, one of the sources of randomness is from the shift in the D.C. current, also known as the burst noise [13]. This phenomenon happens because of the modulation of the current flowing over a physical barrier. The magnitude of this current can be calculated using the Schottky equation, as in (2-2).

$$\overline{\iota^2} = 2qI_D\Delta f \tag{2-2}$$

Where q is the electronic charge,  $I_D$  is the average value of the random current pulses at the drain of the transistor and  $\Delta f$  is the measurement bandwidth. From (2-2), it can be seen that the bigger the bandwidth of the measurement, the higher the current will become. It also suggests that the higher the pulsating current at the drain, the more that the noise will increase. Burst noise is mostly caused by a random variation such as crystallographic defects in the bipolar junction transistor. Impurities can slip into the defect during the manufacturing process and form a low resistance current path. When the current flows over this resistance, some of it will leak, meaning that the output has current inconsistency.

Another source of randomness in semiconductor devices that comes from a random variation in the manufacturing process is the flicker noise. Flicker noise is also known as 1/f noise because it is mainly affecting the lower frequency range, i.e., Megahertz frequency. Two theories can be used to explain the flicker noise phenomenon, namely the number fluctuation theory [14] and mobility fluctuation theory [15]. Number fluctuation theory explains that flicker noise happens because there is an inconsistency in the number of electrons that can pass through the defective current path at any given time. On the contrary, mobility fluctuation theory states that flicker noise does not have any correlation with the number of electrons that pass the defective current path. Still, the velocity inconsistency of those electrons causes this. However, both theories agree that the leading cause of the flicker noise comes from the defective current path of the transistor, which is a random variation of the manufacturing process.

#### 2.3.2 Random Number Generator in FPGA

FPGA refers to embedded electronics comprised of a vast number of digital circuitries known as primitives that can be employed to configure a wide range of different applications. There are two methods of RNG integration for FPGA applications, either through building mathematics models of RNGs using FPGA primitives which results in PRNGs [15] or by utilizing the random variation of the FPGA manufacturing process, thus creating TRNGs [15]. Although FPGA provides a sufficient level of randomness with high throughput for PRNG applications, the random number that it generates is no longer secure if the function behind the PRNG is compromised. This rest of this section focuses on the implementation of TRNG in FPGA.

There are two main components used to build the TRNG in FPGA: the source of randomness and the extractor. First, the source of randomness is the combination of the state space S and transition function f, as in (2-1). The transition function f is to prepare the state space S for generating the next random number.

An example of a digital circuit that can be used as a source of randomness for TRNG when implemented in FPGA is the shift-register. The shift register consists of a chain of flip-flops. With the FPGA from Xilinx, the shift-register can be simplified by utilizing the SRL16E [16] which is a particular mode of the LUT in Xilinx's FPGA. This configuration will significantly reduce silicon area usage.

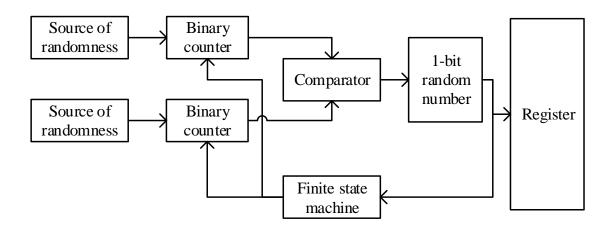

The second component to build TRNG in FPGA is the extractor. One of the easiest ways to create an extractor function in FPGA is by using a comparator circuit to compare the quality of the two sources of randomness. If one source of randomness is better than the other, it will generate bit "1", and if it is the other way around, it will produce bit "0".

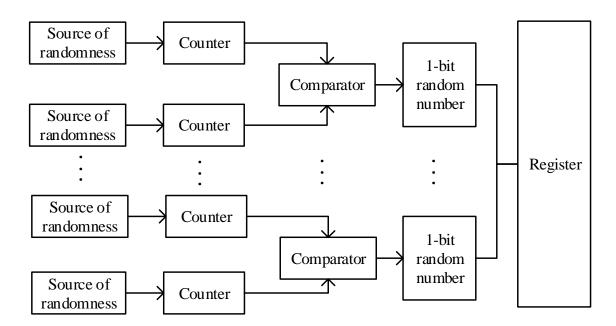

A simplified block diagram of TRNG for the implementation in FPGA is presented in Figure 2-2. The oscillation frequency of the two Sources of Randomness (SoR) will be counted by the binary counter and compared in a comparator circuit to generate the 1-bit random number. The 1-bit random number will be stored in a register and concatenated. After the first random number generation is finished, the finite state machine will tell the counter to start the SoR frequency counting routine again. In order to generate a 128-bit random number, it needs to run 128 times.

Figure 2-2: Block diagram of TRNG implementation

#### 2.3.3 Test for Randomness

There are a couple of concepts that have been proposed in the literature to measure the quality of the bits produced by the random number generator. One of the parameters that can be easily tested with a non-statistical method is the frequency test. The frequency test aims to measure the uniformity of the bits produced by the RNG. An ideal uniform binary random number contains the same number of ones and zeros. This means that it has 50% uniformity while 100% uniformity means that the random number is made up of all ones or all zeros.

Another concept to measure the quality of a random number generator is by using a statistical test. There are a couple of suites used to test the randomness of an RNG such as DieHARD [17], FIPS140-2 [18], AIS-31[19], NIST SP800-22 [20], and TestU01 [21]. Table 2-2 shows the differences between each test suite.

Table 2-2: Minimum Input for Different RNG Test Suites

| Name of the test suite | No. of test types | minimum input<br>(bit) | Year of publication |

|------------------------|-------------------|------------------------|---------------------|

| DieHARD                | 18                | 2.5 million            | 1995                |

| FIPS 140-2             | 11                | 16                     | 2001                |

| AIS-31                 | 9                 | 3 million              | 2001                |

| TestU01                | 266               | 32 (max)               | 2007                |

| NIST SP800-22          | 15                | 1 million              | 2010                |

Every random number test suite measures the p-value of the RNG. The p-value refers to the probability that the RNG under test will have the same quality as the referenced RNG used in the test suite. The p-value is chosen to represent the quality of an RNG to understand whether an RNG is good or bad. Nevertheless, it does not provide any information on which part of the RNG makes it a lousy RNG.

The p-value is compared to a significance level  $\alpha$ , which is set by the tester. If the p-value is lower than  $\alpha$ , then it means that the RNG is rejected as being a good

RNG. For example, the National Institute of Standard and Technologies (NIST) recommends setting the value of  $\alpha$  to 1%. This means that there is a 1% probability that the RNG under test will be as good as the referenced RNG. However, as every RNG test suite is a statistical test, there are two types of error. Type I, also known as a false-positive error, happens when the test suite fails to detect a lower p-value of the RNG under test when it has a small p-value.

On the other hand, type II, also known as a false negative error, happens when the test suite fails to detect a higher p-value of RNG under-test when it has a high p-value. According to [17], a small p-value does not mean that the RNG is terrible. Instead, it tells us that there is a high chance of type II error which is more important from a practical point of view.

George Marsaglia published dieHARD in 1995 as an improvement of a random number of quality measurement techniques developed by Donald Knuth. His idea was to fix the p-value to a pre-chosen interval [ $\alpha$ , 1 –  $\alpha$ ]. Beforehand, the p-value is not fixed, which makes it challenging to interpret the result of the randomness test.

The Federal Information Processing Standard (FIPS) 140-2 is a standard created by NIST in 2001. They also created a new standard called the NIST SP800-22. This is the latest tool used to quantify the quality of a random number generator. The difference between the two is that FIPS is more a qualitative way to standardize a random number generator. In contrast, NIST 800-22 is a more quantitative way to measure a random number generator. However, FIPS140-2 has been criticized by industries because it takes too long to get a random number certified. The certification process cannot be done by the creator of the random number themselves—it must be done by a third-party company.

AIS-31 is an improvised version of FIPS 140-1. It also introduces a new testing technique that focuses on how to measure the quality of a random number that has been post-processed. The tests that are included from FIPS 140-1 are the mono bit test, the poker test, the run test and the most extended run test. The other test used is the autocorrelation test, the uniform distribution test (which

includes 2 sub-tests), a comparative test for a multinomial test and the last one is the entropy test.

TestU01 is considered to be the most comprehensive test as it combines 266 test suites from the existing test suite available in the literature and commercial products. It divides the test into three packs: 1) "Small Crush" which consists of 10 tests, 2) "Crush" with 96 tests and 3) "Big Crush" which consists of 160 tests. However, it only able to handle 32-bit inputs which are too limited for modern RNGs in a cryptographic application.

In this experiment, NIST SP 800-22 Rev. 1a [16] will be used. It is a current standard that is widely used and accepted to measure the randomness of the random number generator. It consists of 15 statistical tests as described in Table 2-3. Every test has several parameters such as minimum bit length (n), block length (m or M), and several sub-tests. The number of n needs to be supplied by the user while m and M are parameters that can be set within the test suite.

Table 2-3: Statistical Tests Within NIST SP 800-22

| TEST NAME                      | n                         | m or M                       |

|--------------------------------|---------------------------|------------------------------|

| Frequency Test                 | <i>n</i> ≥100             | -                            |

| Frequency Test within a Block  | <i>n</i> ≥100             | $20 \le M \le n/100$         |

| Runs Test                      | <i>n</i> ≥100             | -                            |

| Longest-Run-of-Ones            | <i>n</i> ≥128             | -                            |

| Binary Matrix Rank             | <i>n</i> ≥38912           | -                            |

| FFT                            | <i>n</i> ≥1000            | -                            |

| Non-overlapping Template       | <i>n</i> ≥8 <i>m</i> −8   | $2 \le m \le 21$             |

| Overlapping Template           | n ≥10 <sup>6</sup>        | -                            |

| Maurer's Universal Statistical | <i>n</i> ≥387840          | -                            |

| Linear Complexity              | n ≥10 <sup>6</sup>        | $500 \le M \le 5000$         |

| Serial Test                    |                           | $2 < m < [\log 2 \ n] - 2$   |

| Approximate Entropy            |                           | <i>m</i> <[log2 <i>n</i> ]−5 |

| Cumulative Sums                | 100                       | -                            |

| Random Excursions              | <i>n</i> ≥10 <sup>6</sup> | -                            |

| Random Excursions Variant      | <i>n</i> ≥10 <sup>6</sup> | -                            |

NIST SP800-22 is widely used in industry and commercial RNG products because it is considered as having a low tolerance to error. Because of this, it is hard to pass the NIST SP800-22 unless the RNG is perfect. This claim is confirmed by [17], which mentions that high numbers of good RNG have difficulty passing 20% of the NIST test.

#### 2.3.4 Metrics

Cryptography applications need a high rate of random number generation. The parameter used to measure the rate of the random number generation is known as the throughput. Throughput is calculated using (2-3).

$$throughput = \frac{n \times f_{max}}{latency} \tag{2-3}$$

where n is the number of bit-length of the generated random number,  $f_{max}$  is the maximum working frequency of the design, and latency is the number of cycles taken to generate the 1 bit of random number.  $f_{max}$  is obtained by looking at the post-route-and-placement report of the FPGA and not the maximum frequency of the FPGA board.

## 2.4 Experimentation

## 2.4.1 Design of Ring Counter RNG (RCRNG)

The RNG based on the ring counter circuit will be implemented in the Kintex-7 FPGA development board, which consists of 7K325T FPGA from Xilinx. It utilizes 28 nm technology which is still widely used in critical systems nowadays, such as in avionics and radar technology. The Kintex-7 FPGA is categorized as a −2L device, means that it has a nominal voltage of 0.9 Volts. It is understandable that the threshold voltage for 28 nm devices is 0.4 Volts, and the experiment should

ideally run at that voltage level. However, this experiment uses the nominal voltage of the FPGA because lowering the voltage beyond the recommended voltage can harm the FPGA. While the differences between the nominal voltage used and the threshold voltage is an exciting topic to discuss, this experiment is focused on the effect of the non-uniform distribution of the process variation caused by the near-threshold voltage to the delay-based TRNG. This will leave the research on the environmental impacts, such as voltage and temperature differences, to others.

In this experiment, SRL16E will be used as the primary source of randomness for TRNG. The motivation behind it is to test the feasibility of upcoming silicon technology where the size of the transistor will become smaller. As stated in [16], LUT in SRL16E mode has very short wiring, so the delay should be slight enough to affect the timing or power consumption. This property will be used as the model for future delay-based TRNGs in FPGAs where the wiring is tiny. However, the differences in the delay are too small to be measured with today's technology. Therefore, in this experiment, the configuration of the shift-register from SRL16E for creating the ring counter is used. A ring counter is a shift-register with a feedback loop. The introduction of the loop will increase the delay to the measurable value of today's measurement technology.

The main component to build the RC-based TRNG is sliceM. It contains LUTs that can be programmed as a 16-bit shift-register in the form of SRL16E from the UNISIM library. By instantiating the LUT as shift-register, the resource usage of FPGA can be minimized.

The idea of using a ring counter as a source of randomness for TRNG is the same as the idea of using a ring oscillator to create a delay of a system clock. Two ring counters initialized as 10101010.... or 01010101010... will oscillate when activated. Depending on the process variation of the components used to create the ring counter, the oscillation frequency will be different from one ring counter to another. A 1-bit random number can be generated by comparing the frequency of two ring counters. In this experiment, the 16-bit ring counter was initialized only to have one bit of 1 and 15 bits of 0. This configuration was used to create a more

significant delay, so then the signal analyzer can easily see the difference in frequency. However, this configuration will increase the latency of the design and affect the overall throughput.

The TRNG is built based on the block diagram shown in Figure 2-2 without the finite state machine. This configuration is then stacked in parallel, as in Figure 2-3. The reason for this is that by using a parallel configuration, it is possible to generate an n-bit of random numbers in one run. This configuration also increases the confidence level of the measurement and the bit generation because it minimizes the effect of temperature and voltage change.

Figure 2-3: Block diagram of TRNG implementation

#### 2.4.2 Experimental Limitation

Before implementing the RCRNG, there are a couple of things that need to be considered. The first is to find the location on the FPGA floorplan where the pair of RCs that will be compared can produce the best entropy for the random number generator. This can be done by inspecting every possible location in the FPGA floorplan. After that, every likely pair of RCs also needs to be checked to

find the best entropy. However, there are 16000 sliceMs in Kintex-7 7K325T FPGA. A single sliceM consists of 4 LUT that can be programmed as a four 16-bit shift register (SRL16E). Therefore, there are  $2^4 = 16$  possible combinations on a single sliceM. Testing all of the possible combinations of all of the potential locations means to test 256.000 possible combinations, which will be time-consuming. Therefore, some constraint needs to be applied to the experiment by limiting the number of RC pairs that will be tested as follows:

- 1. The test will only be done by comparing the neighbouring LUTs on the same slice. This makes it only possible to compare two pairs of LUT per sliceM.

- 2. To acquire the data, an integrated logic analyser, in this case, Chipscope Pro 14.7, was used. Even though it is a powerful tool to debug the circuit design of FPGA, there are some practical limitations. For Kinetix-7 FPGA, the maximum number of signals that it can read at a single time is 4096. Hence in order to test all the possible pairs by applying the constraint on point 1), the measurement needs to be done (16 x 16000)/4096 times, or about 62 times, which is a time-consuming process. For this reason, the test will be limited to as close as to the maximum number of signals of Chipscope as possible, which is 4000 RC pair. Each pair will be captured 1000 times in order to be able to understand the uniformity of the ring counter pair.

- 3. The process of placement will be done manually by applying the location constraint to the ring counter pair and the relative location constraint to the counter, so then it is located close to the ring counter.

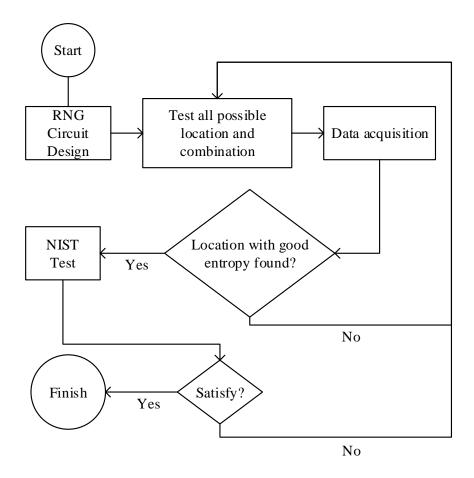

Even though there are some limitations in this experiment, it still gives a clear idea about the steps needed to find the best location for the RC pair to generate a random number with the best entropy. The flowchart in Figure 2-4 is given for a better understanding of the location selection process.

Figure 2-4: Location selection flowchart

Secondly, concerning the more technical aspect of the design, the delay in every part of the circuit needs to be the same up to the counter logic. In FPGA, the delay on the ring counter is not a problem, and it is assumed to be the same. This is because, in FPGA, the ring counter was made by instantiating a LUT which means that no wiring is needed to connect the component that builds the ring counter. However, it is a bit of a challenge to make sure that the delay between the ring counter and the counter is the same. This is because the manual routing tool from ISE is complicated to use. Therefore in this experiment, the delay from the ring counter to the counter is made as small and as similar as possible by forcing the placement of the counter to be as close as possible relative to the ring counter circuit.

Lastly, it is desirable to create a hard macro of the RCRNG circuit (at least from ring counter to counter circuit) to fix the location, to lessen any delays between the components and to make sure that there is no additional logic inserted into the circuit. However, it remains a big challenge for FPGA designers to create a hard macro from an instance that has an initialization value in one of the components of the hard macro. In this case, the ring counter circuit needs to have an initial value which will have consequences on the presence of a power net. In ISE 14.7, the tool does not accept any power nets inside a hard macro. In this experiment, to make sure that there is no additional logic added to the path between the ring counter and the counter, they need to be forcibly located as close as possible relative to the ring counter circuit. This can be done by using rloc constraint.

## 2.5 Findings and Analysis

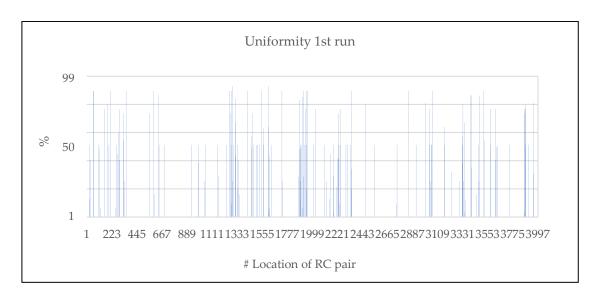

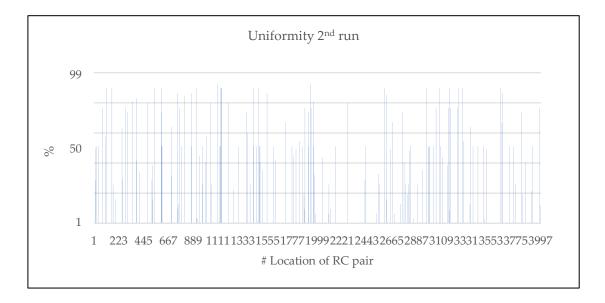

From the 4000 pairs of the ring counter, the uniformity of the bits generated from each RC pair can be calculated. In Figure 2-5, the RC pair that have 100% uniformity is not shown to clarify the graph. Perfect uniformity in a bit string is reached when the number of ones is the same as the number of zeros, indicating that the uniformity is 50%. From Figure 2-5, there are 45 RC pairs that have precisely 50% uniformity. However, the initial design was to create a 128-bit random number. Therefore another run of tests is needed to find the RC pairs that have 50% uniformity. After undertaking the process for another two times, 32 and 55 RC pairs were found after the second and third location finding process, as shown in Figure 2-6 and Figure 2-7. In total, 132 locations with 50% of uniformity were found which is sufficient to build the 128-bit RNG.

Figure 2-5: Uniformity of the RC pairs on the first run

Figure 2-6: Uniformity of the RC pairs on the second run

Figure 2-7: Uniformity of the RC pairs on the third run