# Robust Time Synchronization for Industrial Internet of Things by $H_{\infty}$ Output Feedback Control

Yan Zong<sup>®</sup>, Member, IEEE, Xuewu Dai<sup>®</sup>, Member, IEEE, Zhuangkun Wei<sup>®</sup>, Mengbang Zou<sup>®</sup>, Weisi Guo<sup>®</sup>, Senior Member, IEEE, and Zhiwei Gao<sup>®</sup>, Senior Member, IEEE

Abstract—Precise timing over timestamped packet-exchange communication is an enabling technology in the mission-critical industrial Internet of Things (IIoT), particularly when satellite-based timing is unavailable. The main challenge is to ensure timing accuracy when the clock synchronization system is subject to disturbances caused by the drifting frequency, time-varying delay, jitter, and timestamping uncertainty. In this work, a robust packet-coupled oscillators (R-PkCOs) protocol is proposed to reduce the effects of perturbations manifested in the drifting clock, timestamping uncertainty, and delays. First, in the spanning-tree clock topology, time synchronization between an arbitrary pair of clocks is modeled as a state-space model, where clock states are coupled with each other by one-way timestamped packet exchange (referred to as packet coupling), and the impacts of both drifting frequency and delays are modeled as disturbances. A static output controller is adopted to adjust the drifting clock. The  $H_{\infty}$  robust control design solution is proposed to guarantee that the ratio between the modulus of synchronization precision and the magnitude of the disturbances are always less than a given value. Therefore, the proposed time synchronization protocol is robust against the disturbances, which means that the impacts of drifting frequency and delays on the synchronization accuracy are limited. The one-hour experimental results demonstrate that the proposed R-PkCO's protocol can realize time synchronization with the precision of 6  $\mu$ s in a 21-node IEEE 802.15.4 network. This work has widespread impacts in the process automation of automotive, mining, oil, and gas industries.

Index Terms— $H_{\infty}$  control, packet-coupled oscillators (PkCOs), pulse-coupled oscillators (PCO), time synchronization, wireless sensor networks.

## I. INTRODUCTION

VER the last decade, the rapid proliferation of Internet of Things (IoT) has been instrumental in the digital manufacturing revolution (fourth industrial revolution), and a new era of the Industrial IoT (IIoT) has emerged with different requirements to traditional IoT systems. Precise timing is one of the most sought after IIoT attributes in mission-critical

Manuscript received 31 October 2021; accepted 5 January 2022. Date of publication 18 January 2022; date of current version 24 January 2023. (Corresponding author: Xuewu Dai.)

Yan Zong, Zhuangkun Wei, Mengbang Zou, and Weisi Guo are with the School of Aerospace, Transport and Manufacturing, Cranfield University, Cranfield MK43 0AL, U.K. (e-mail: y.zong@cranfield.ac.uk; zhuangkun.wei@cranfield.ac.uk; m.zou@cranfield.ac.uk; weisi.guo@cranfield.ac.uk).

Xuewu Dai and Zhiwei Gao are with the Department of Mathematics, Physics and Electrical Engineering, Northumbria University, Newcastle upon Tyne NE7 7YT, U.K. (e-mail: xuewu.dai@northumbria.ac.uk; zhiwei.gao@northumbria.ac.uk).

Digital Object Identifier 10.1109/JIOT.2022.3144199

industrial applications, especially those that have control loops commonly found in chemical engineering and precision manufacturing. This means that the time-sensitive wireless IIoT networks have stringent requirements on the reliability and the real time of data transmission and control operation command [1], [2]. Hence, the enabling technology time synchronization is required to provide a common sense of timing among wireless nodes.

Due to the inherent low energy consumption [3] and reliability [4] characteristics of spanning-tree topology, it has been widely used for time synchronization [5]. Also, inspired by the synchrony of fireflies' flashing [6], a typical model, pulse-coupled oscillators (PCO), is proposed in natural and physical science communities [7]. Thanks to its simplicity and scalability, this model is particularly suitable for resource-constrained wireless sensor networks [8]. However, the assumptions of PCO (e.g., failure of producing the physical *Pulse* signal, and no delays exist during the firing information (i.e., *Pulse*) exchange among oscillators) limit its application in off-the-shelf wireless networks. Thus, it needs to be improved for employment in industrial applications.

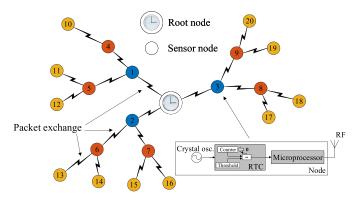

In IEEE 802.15.4 (also known as ZigBee) [9] networks, the PCO's *Pulse* waveform cannot be generated from the medium access control (MAC) layer. Nevertheless, the wireless packet can be treated as a substitute solution for the *Pulse* signal. Moreover, the periodic resetting feature of the clock model is similar to the firing-resetting procedure in PCO [10]. Therefore, our earlier work [11] proposed the packet-coupled oscillators (PkCOs) model, where the *Sync* packet (from a transmitter) is utilized for reporting the firing information to other nodes. In this work, we utilize the  $H_{\infty}$  method for selecting the PkCOs [11] parameters. Thus, a robust PkCOs (R-PkCOs) protocol is proposed for the spanning-tree clock synchronization network (e.g., Fig. 1).

# A. Related Work

As a result of the widespread importance of synchronization, it has been studied in various communities, and many synchronization protocols have been proposed for wireless networks. In the communication engineering community, from the perspective of the packet-exchange strategy, these algorithms can be categorized into two types, which are the

<sup>1</sup>We refer the reader to Section II for more details of Fig. 1.

2327-4662 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 1. Spanning-tree clock synchronization network.

receiver-to-receiver (e.g., RBS [12]) and sender-to-receiver<sup>2</sup> (e.g., TPSN [13], RMTS [14], and PISync [15]) synchronization protocols. The principle of these algorithms is to measure the clock offset (which is referred to as the time difference between two connected clocks) through packet exchange during each synchronization cycle T; and the employment of the offset estimate to the local clock lets a network achieve time synchronization.

For the RBS and TPSN algorithms, during a cycle *T*, several timestamped packets are sent and received between a pair of nodes. However, once these two protocols are employed to the large-scale wireless network, the offset estimate suffers from a delay jitter, owing to factors, such as packet collisions and retransmission. Utilizing inaccurate offset estimates reduce the synchronization performance of RBS and TPSN in the multihop network. In addition, since the radio frequency (RF) transceiver is the most power consumption unit in a wireless node [16], frequent RF communication poses a challenge on the energy-constrained node.

In many mission-critical industrial applications, the slot-based contention-free packet transmission mechanism is used to guarantee that the packet-exchange delay is almost deterministic, and thus to ensure a high Quality of Service (QoS) [11], [17]. Thanks to this feature, instead of transmitting multiple wireless packets, the one-way sender-to-receiver protocol (also referred to as the flooding algorithm) only needs one packet to obtain a more accurate clock offset, thereby leading to better synchronization precision. Moreover, two timestamps are required in the flooding algorithm: one is generated when a transmitter sends a packet, and the other one is on the reception of the packet on a receiver.

The IEEE 802.15.4 standard provides the beacon-enabled operation on the MAC layer, and the corresponding superframe [consisting of contention access period (CAP), contention-free period (CFP), and inactive period] offers hybrid transmission mechanisms. Specifically, during CAP, all nodes need to contend for the access of a frequency channel. Instead, the CFP guarantees a specific slot to each node. The control packet (i.e., *Sync*) of R-PkCOs is sent in CFP to guarantee low-latency

transmission and a tiny jitter. Furthermore, the R-PkCO's protocol only demands one timestamp (which is generated upon the reception of a *Sync* packet), and the packet itself represents the clock firing information. This feature can further reduce the effects of timestamping uncertainty, improve offset estimate accuracy, and enhance synchronization performance, compared to the flooding protocol.

In addition to the packet-exchange strategy, using advanced processing techniques (e.g., maximum-likelihood estimation [18], and linear least squares regression [19]) is an alternative way to improve time synchronization precision. Typically, the clock frequency difference may let the achieved synchronization lose gradually [20]. The clock skew<sup>3</sup> correction method allows the longer synchronized state and the less frequent strychninization among coupled clocks.

In [14] and [18], the maximum-likelihood estimation method is used to estimate the clock skew and also to obtain a more accurate clock offset; however, the resource-limited node (with a 32-bit microprocessor) has difficulty in handling such a complex processing technology. Thus, in [19], the estimation procedure of clock offset and skew via the linear least squares regression method is on the cluster head, which is equipped with a powerful processor, rather than on the local node. Even though Tian *et al.* [21] adopted the lower computational complexity solution (i.e., exponential moving average) to calculate the clock skew, the proposed synchronization algorithm is still evaluated on FPGA-based wireless nodes. Moreover, Yildirim et al. [15] stated that a proportional-integral controller is utilized in PISync, from (3) and (6) of this cited work, the used controlling strategy actually is a proportional controller. In this article, a static output feedback controller is adopted for clock correction, and it demands fewer computational overhead, compared to the above processing methods (e.g., [18] and [21]).

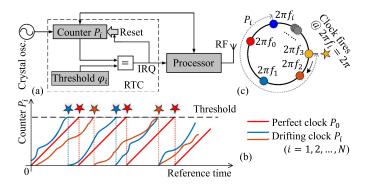

It is notable that, although the works cited above take the nonidentical [14], [21] and drifting [15] clock frequency, and packet-exchange delay [11], [14], [15], [21] into consideration, only the theoretical analysis of a synchronization protocol is presented. In addition, the logical (or virtual) clock, which is an affine function of the physical clock in Fig. 2(a), is used in the protocol analysis and hardware experiments [14], [15], [21]. Thus, the processing delay, which occurs during the data processing, and the employment of offset and skew estimates, are missing. Overall, there still exists a lack of theoretical design of synchronization protocol parameters, with the effects of clock noises and external disturbances (from packet-exchange and processing delays). This motivates us to use the  $H_{\infty}$  control solution for parameter selection of the R-PkCOs protocol and extending our previous researches [8], [11].

#### B. Contributions and Paper Organization

In this article, we propose a robust PkCOs protocol to correct both clock skew and offset for improving synchronization precision, subject to the impacts of drifting frequency, and

<sup>&</sup>lt;sup>2</sup>The sender-to-receiver synchronization algorithm can be further classified into two kinds, namely, the one-way (e.g., RMTS and PISync) and two-way (e.g., TPSN) exchange protocols.

<sup>&</sup>lt;sup>3</sup>The skew is defined as the normalized difference between two clock frequencies, see (3) of Section II.

Fig. 2. (a) Structure of an RTC module. (b) Dynamics of the counter register in the RTC module. (c) PkCOs.

external perturbations from delays. In addition to using the slot-based one-way Sync packet transmission mechanism, the  $H_{\infty}$  control method is also adopted to guide the R-PkCOs parameter selection, for letting clock and delay noises possess a small effect on the synchronization accuracy. Specifically, through designing the static controller, the ratio between the modulus of the achieved synchronization precision and the magnitude of the noises is always less than a given value. Thus, the robustness of R-PkCOs is guaranteed, in the presence of internal clock and external delay noises. The one-hour experimental results show that the proposed R-PkCOs protocol is capable of achieving time synchronization with the precision of 6 ms in a spanning-tree clock network.

The remainder of this article is organized as follows. Section II describes the R-PkCOs model, which consists of the mathematical modeling of a nonidentical and drifting embedded clock, and the packet-coupled synchronization scheme. Then, Section III presents the  $H_{\infty}$  output feedback control for the R-PkCOs time synchronization method. The simulation and experimental results are, respectively, shown in Sections IV and V. Eventually, Section VI concludes this work.

# II. ROBUST PACKET-COUPLED OSCILLATORS

The spanning-tree clock synchronization network, for example, in Fig. 1, can be described by a directed graph  $\mathcal{G} = (\mathcal{V}, \mathcal{E}, \mathcal{A})$ , where  $\mathcal{V} = \{0, 1, \dots, N\}$  denotes a set of nodes, and a set of edges  $\mathcal{E}$  induced by the adjacency matrix  $\mathcal{A}$ . The network is composed of a root node (i.e., i = 0) and a set of sensor nodes represented by  $\mathcal{N} = \{i : i \in \mathcal{V}, i \geq 1\}$ . The root node is unique and is equipped with a global positioning system (GPS) clock to provide the reference time to all the sensor nodes in a network. For the *i*th sensor node, it corrects the local clock, upon the reception of a *Sync* packet from the parent node.

# A. Modeling of Drifting Embedded Clocks

In the embedded system, the real-time clock (RTC) module of each node is implemented by a counter register, which is driven by a crystal oscillator [see Fig. 2(a)]. As shown in Fig. 2(b), once the counter reaches the predefined value in the threshold register, it is reset and counts from zero again; in the meantime, an interrupt (i.e., IRQ) signal is sent to the processor for triggering an event (e.g., sending a wireless packet for synchronization purposes). This periodic resetting feature can be modeled as an oscillator running on the unit circle [see Fig. 2(c)]. Once the oscillator's time variable  $P_i$  reaches the threshold, the oscillator fires (i.e., a *Sync* packet is generated and transmitted in CFP) and  $P_i$  are reset to zero, after which it increases again. Note that since *Sync* itself contains the clock firing information, there is no need to generate a timestamp when sending the packet. This helps R-PkCOs reduce the effects of timestamping uncertainty.

Referring first to the case of an ideal embedded clock on the root node, the time variable  $P_0[n]$  can be utilized to model the clock's periodic resetting behavior, and  $P_0[n]$  at the nth event satisfies the following form:

$$P_0[n] = n\tau_0 - \sum_{h=0}^{k} \varphi_0[h] \tag{1}$$

where  $\tau_0$  is the nominal (clock update) period, and the nominal frequency  $f_0$  of the perfect clock is equal to  $f_0 = 1/\tau_0$ .  $\varphi_0[k]$  is the clock's threshold; in practice,  $\varphi_0[k]$  may be a constant value, which equals the time synchronization cycle T. k is the number of clock resetting from n=0 to the nth event, and it also represents that the clock is at the kth synchronization cycle. In addition, we assume that the perfect clock updates  $m_0$  times in a cycle T (i.e.,  $\varphi_0 = m_0 \tau_0$ ) [11]. Thus, k can be obtained from the floor function  $k = \lfloor n/m_0 \rfloor$ .

However, due to the manufacturing tolerance and environmental temperature, the *i*th clock's time variable  $P_i[n]$  cannot be the same as  $P_0[n]$  of the perfect clock. Through modeling the random noise from the phase variation  $\phi_i[n]/2\pi f_0$  and the clock frequency deviation  $\chi_i[n] = f_i[n] - f_0[10]$ ,  $P_i[n]$  is

$$P_i[n] = n\tau_0 + \frac{\sum_{h=0}^{n-1} \chi_i[h]\tau_0}{f_0} + \frac{\phi_i[n]}{2\pi f_0} - \sum_{h=0}^k \varphi_i[h]$$

(2)

where  $\varphi_i[k]$  is the *i*th clock threshold.  $\varphi_i[k]$  is assumed to equal  $\varphi_0[k]$  during the clock modeling.

Let the clock offset  $\theta_i[n]$  represent the difference between  $P_i[n]$  and  $P_0[n]$ . The clock skew  $\gamma_i[n]$  is referred to as the normalized difference between  $f_i[n]$  and  $f_0$ . Hence,  $\theta_i[n]$  and  $\gamma_i[n]$  are, respectively, given by

$$\theta_i[n] = P_i[n] - P_0[n], \quad \gamma_i[n] = \frac{\chi_i[n]}{f_0}.$$

(3)

By substituting (1) and (2) into (3), calculating the offset difference between two consecutive clock events and expanding the clock offset and skew from n-dimension into k-dimension [22], the drifting embedded clock (2) is remodeled as

$$\begin{cases} \theta_i[k+1] = \theta_i[k] + \gamma_i[k]T + \omega_{\theta_i}[k] \\ \gamma_i[k+1] = \gamma_i[k] + \omega_{\gamma_i}[k] \end{cases}$$

(4)

where  $\omega_{\theta_i}[k]$  and  $\omega_{\gamma_i}[k]$  are the Gaussian random noise processes, and the corresponding variances are  $\sigma_{\theta_i}^2$  and  $\sigma_{\gamma_i}^2$  [23]. The matrix form of (4) is also obtained

$$x_i[k+1] = Ax_i[k] + \omega_i[k] \tag{5}$$

<sup>&</sup>lt;sup>4</sup>To guarantee high performance, the node with a more accurate timing (e.g., the root node in Fig. 1) drives the cascade synchronization, and no reverse driving exists.

where  $x_i[k] = [\theta_i[k], \gamma_i[k]]^T$  represents the *i*th clock state vector.  $\omega_i[k] = [\omega_{\theta_i}[k], \omega_{\gamma_i}[k]]^T$  is the *i*th clock noise process vector. The matrix A is equal to  $A = \begin{bmatrix} 1 & T \\ 0 & 1 \end{bmatrix}$ .

## B. Packet-Coupled Synchronization Scheme

In order to reduce the effects of packet-exchange delay jitter on the synchronization precision, this work allocates the *Sync* packet transmission event to a specific time slot (in CFP) for synchronizing drifting embedded clocks. To be specific, at the kth time synchronization cycle, upon the reception of a *Sync* packet (which is from node j and is transmitted at the time slot  $t_{kj}$ ) after the packet-exchange delay  $\kappa_{ij}[k]$ , node i generates a timestamp  $\hat{P}_i[k]$  via reading the counter register

$$\hat{P}_i[k] = P_i \left( t_{k_i} + \kappa_{ij}[k] \right) \tag{6}$$

where  $\kappa_{ij}[k]$  is the Gaussian random process with the mean of  $\bar{\kappa}_{ij}$  and the variance of  $\sigma_{\kappa_{ij}}^2$  [11], [14].

Next, the utilization of the local timestamp  $\hat{P}_i[k]$  can calculate the offset estimate  $\hat{\theta}_i[k]$ , following:

$$\hat{\theta}_i[k] = \theta_i (t_{k_i} + \kappa_{ij}[k]). \tag{7}$$

In the meantime, the skew estimate is obtained from  $\hat{\gamma}_i[k] = (\hat{\theta}_i[k] - \hat{\theta}_i[k-1]^+)/T$ , where  $\hat{\theta}_i[k-1]^+$  is the offset after the ith embedded clock is adjusted at the (k-1)th cycle. Even though  $\hat{\theta}_i[k-1]^+$  is unknown, the clock offset approaches to zero at the synchronized state. Thus, we assume that the clock offset is perfectly corrected, and  $\hat{\theta}_i[k-1]^+$  is zero. The skew estimate  $\hat{\gamma}_i[k]$  is calculated from

$$\hat{\gamma}_i[k] = \frac{\hat{\theta}_i[k]}{T}.$$

(8)

Instead of employing the complete offset and skew estimates to a drifting clock, this article utilizes a static controller to improve synchronization performance, yielding

$$\begin{cases} u_{\theta_i}[k] = \alpha \left( r_{\theta_i} - \hat{\theta}_i[k] \right) \\ u_{\gamma_i}[k] = \beta \left( r_{\gamma_i} - \hat{\gamma}_i[k] \right) \end{cases}$$

(9)

where  $u_{\theta_i}[k]$  and  $u_{\gamma_i}[k]$  are the offset and skew correction inputs, respectively.  $r_{\theta_i}$  and  $r_{\gamma_i}$  are, respectively, the offset and skew reference inputs.  $\alpha$  and  $\beta$  are the controller's parameters.

Practically, due to limitations of the processor architecture, the processing delay  $\eta_i[k]$  occurs, when the offset correction input  $u_{\theta_i}[k]$  is applied to the counter register [8]. The clock's time variable actually is adjusted at the time  $t_{k_i} + \kappa_{ij}[k] + \eta_i[k]$

$$P_{i}[k]^{+} = P_{i}(t_{k_{i}} + \kappa_{ij}[k] + \eta_{i}[k]) + \left(u_{\theta_{i}}[k] + \bar{\eta}_{i}\right)$$

(10)

where the processing delay  $\eta_i[k]$  is the Gaussian random process with the mean of  $\bar{\eta}_i$  and the variance of  $\sigma_{\eta_i}^2$ . The extra value of processing delay is unintentionally employed to correct the local clock, and the effects of timestamping uncertainty are modeled in  $\eta_i[k]$  [11]. This work compensates for the impacts of this processing delay via adding its mean value to  $u_{\theta_i}[k]$ , as shown in [8].

From (3), the employment of offset correction input  $u_{\theta_i}[k]$  is equivalent to the clock correction action on  $\theta_i[k]$ . That is

$$\theta_i[k]^+ = \theta_i \left( t_{k_j} + \kappa_{ij}[k] + \eta_i[k] \right) + \left( u_{\theta_i}[k] + \bar{\eta}_i \right). \tag{11}$$

To correct the clock skew, the following expression is used:

$$\gamma_i[k]^+ = \gamma_i(t_{k_i}) + u_{\gamma_i}[k].$$

(12)

Remark 1: The packet-exchange delay  $\kappa_{ij}[k]$  is almost deterministic, owing to the slot-based Sync packet transmission in CFP. The employment of  $\bar{\kappa}_{ij}$  eliminates the effects of  $\kappa_{ij}[k]$  [11]. Thus, in the experiments,  $\hat{\theta}_i[k]$  of (9) is calculated from

$$\hat{\theta}_{i}[k] = \begin{cases}

\hat{P}_{i}[k] - \bar{\kappa}_{ij} + \Delta t_{d_{ij}}, & \text{if } \hat{P}_{i}[k] - \bar{\kappa}_{ij} + \Delta t_{d_{ij}} < \frac{\varphi_{i}[k]}{2} \\

\hat{P}_{i}[k] - \bar{\kappa}_{ij} + \Delta t_{d_{ij}} - \varphi_{i}[k], & \text{if } \hat{P}_{i}[k] - \bar{\kappa}_{ij} + \Delta t_{d_{ij}} \ge \frac{\varphi_{i}[k]}{2}

\end{cases}$$

(13)

where  $\Delta t_{dij} = t_{di} - t_{dj}$  is the difference of anti-phase synchronization duration between nodes i and j, and the anti-phase synchronization duration  $t_{di}$  is defined by  $t_{di} = \begin{cases} 0, & \text{if } i = 0 \\ t_{dp} + (i-1)t_{sd}, & \text{if } i \geq 1 \end{cases}$ ,  $t_{dp}$  means the contention access period, and the application data stream can be sent during this CAP.  $t_{sd}$  represents the slot duration.

For the purpose of realizing collision-free packet transmission in CFP,  $r_{\theta_i}$  and  $r_{\gamma_i}$  are, respectively, set to  $-\Delta t_{d_{ij}}$  and 0 to allocate the slot  $t_{d_i}$  for node i. Once a network system is at the steady synchronized state, the ith clock offset  $\theta_i[k]$  approaches  $t_{d_i}$  to realize the scheduling of wireless Sync packets, and  $\gamma_i[k]$  converges to zero to achieve synchronization of drifting clocks. This Sync scheduling solution can help decrease the packet-exchange delay jitter, thereby improving synchronization precision.

Remark 2: Due to the difficulty of adjusting embedded clock frequency, in the experiments, the clock threshold correction is utilized as a substitute approach for the frequency adjustment, yielding

$$\varphi_i[k+1] = \varphi_i[k] + u_{\varphi_i}[k] \tag{14}$$

where the threshold correction value  $u_{\varphi_i}[k]$  is equal to  $u_{\varphi_i}[k] = -\beta(r_{\gamma_i} - \hat{\theta}_i[k])$ .

#### III. ROBUST OUTPUT FEEDBACK CONTROLLER

Apart from reducing packet-exchange delay jitter via the slot-based transmission mechanism, we also adopt the  $H_{\infty}$  control solution to let clock and delay noises possess a small impact on the accuracy, which further improves synchronization performance. This section starts by presenting the state-space representation of a static output feedback controller. Then, the  $H_{\infty}$  control is utilized to design the R-PkCOs parameters, thus guaranteeing the robustness of the proposed method in a spanning-tree clock synchronization network.

#### A. Output Feedback Controller in State Space

In contrast to the conventional continuous control system with delays, delays play a different role in the discrete time synchronization system. This means that the impacts of packet-exchange and processing delays of the synchronization system can be decoupled from the temporal dimension and are represented as biases or disturbances in the variable  $P_i$

dimension [11]. The effects of packet-exchange delay in the temporal dimension can be removed by subtracting  $\bar{\kappa}_{ij}$  from the timestamp  $\hat{P}_i[k]$  [8]. Thus, (7) and (8) are rewritten as

$$\begin{cases} \hat{\theta}_i[k] = \theta_i[k] + \nu_{\theta_i}[k] \\ \hat{\gamma}_i[k] = \gamma_i[k] + \nu_{\gamma_i}[k] \end{cases}$$

(15)

where  $v_{\theta_i}[k] = \kappa_{ij}[k] + \delta_{\kappa_{ij}}[k] - \bar{\kappa}_{ij}$  is the offset measurement noise with the mean of  $\bar{v}_{\theta_i}$  and the standard deviation of  $\sigma_{v_{\theta_i}}$ .  $v_{\gamma_i}[k] = (\kappa_{ij}[k] + \delta_{\kappa_{ij}}[k] - \bar{\kappa}_{ij})/T$  is the clock skew measurement noise with the mean of  $\bar{v}_{\gamma_i}$  and the standard deviation of  $\sigma_{v_{\gamma_i}}$ .  $\delta_{\kappa_{ij}}[k]$  and  $\delta_{\eta_i}[k]$  are the extra offset values, which are the joint impacts of clock skew and the length of corresponding (packet-exchange and processing) delays. Let  $y_i[k] = [\hat{\theta}_i[k], \hat{\gamma}_i[k]]^T$ ,  $v_i[k] = [v_{\theta_i}[k], v_{\gamma_i}[k]]^T$ , according to (15), the matrix-vector measurement equation is obtained

$$y_i[k] = C_2 x_i[k] + v_i[k]$$

(16)

where  $y_i[k]$  is the clock output vector.  $v_i[k]$  is the measurement noise vector.  $C_2$  is a 2 × 2 identity matrix.

Likewise, (9) is also modified to the following form via defining the control vector  $u_i[k] = [u_{\theta_i}[k], u_{\gamma_i}[k]]^T$ :

$$u_i[k] = K(r_i - y_i[k])$$

(17)

where  $r_i = [r_{\theta_i}, r_{\gamma_i}]^T$  is a reference input matrix. The gain matrix is equal to  $K = \begin{bmatrix} \alpha & 0 \\ 0 & \beta \end{bmatrix}$ .

For the purposes of theoretical study, (11) and (12) are rewritten as

$$x_i[k]^+ = x_i[k]^- + u_i[k] - \digamma_i[k]$$

(18)

where  $F_i[k] = [(\eta_i[k] + \delta_{\eta_i}[k]) - \bar{\eta}_i, 0]^T$  is the processing delay noise vector [11].

Through applying  $u_i[k]$  to the *i*th embedded clock model (5), it is modified to

$$x_i[k+1] = Ax_i[k] + Bu_i[k] + Ed_i[k]$$

(19)

where the disturbance vector  $d_i[k] = [\omega_i^T[k], v_{ij}^T[k], (\eta_i[k] + \delta_{\eta_i}[k]) - \bar{\eta}_i]^T$  consists of internal clock noises and external perturbations (from packet-exchange and processing delays). B is a  $2 \times 2$  identity matrix. The matrix E is equal to  $E = \begin{bmatrix} 1 & 0 & 0 & 0 & -1 \\ 0 & 1 & 0 & 0 & 0 \end{bmatrix}$ .

Eventually, the pairwise output feedback control synchronization system is given by

$$\begin{cases} x_{i}[k+1] = Ax_{i}[k] + Bu_{i}[k] + Ed_{i}[k] \\ o_{i}[k] = C_{1}x_{i}[k] + Fd_{i}[k] \\ y_{i}[k] = C_{2}x_{i}[k] + Hd_{i}[k] \\ u_{i}[k] = K(r_{i} - y_{i}[k]) \end{cases}$$

(20)

where  $o_i[k]$  is the performance output vector. The matrices  $C_1$ , F, and H are, respectively, equal to

$$C_1 = \begin{bmatrix} 1 & 0 \end{bmatrix}, F = \begin{bmatrix} 0 & 0 & 1 & 0 & 0 \end{bmatrix}$$

$$H = \begin{bmatrix} 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 \end{bmatrix}.$$

As shown in (20), time synchronization is described as a state-space model, whose output is synchronization precision  $o_i[k]$ . In addition, this model is also disturbed by clock and

delay noises  $d_i[k]$ . The purpose of the  $H_{\infty}$  control is to let  $d_i[k]$  possess a tiny impact on the output accuracy  $o_i[k]$ . In other words, by designing the static controller, the ratio between the modulus of the achieved synchronization precision and the magnitude of the noises is always less than a given value.

## B. Controller Optimization

Here, we propose a design condition to guarantee that the networked system is robust in the presence of disturbances (i.e.,  $d_i[k]$ ), caused by the drifting clock, and packet-exchange and processing delays. Mathematically speaking,  $G[z] = C_1(zI-A)^{-1}E+F$  is the transfer function of (20) relating  $d_i[k]$  to  $o_i[k]$ . The performance  $H_{\infty}$  of (20) is guaranteed (i.e.,  $\sup_{\|d_i\|_2 \le 1} \|o_i\|_2 < \rho$ ), if the infinity norm  $\|G[z]\|_{\infty}$ , equalling the two-norm ratio between  $o_i[k]$  and disturbances  $d_i[k]$ , is less than  $\rho$ . That is

$$||G[z]||_{\infty} = \sup_{\|d_i\|_2 \le 1} ||o_i||_2$$

=

$$\frac{||o_i||_2}{||d_i||_2} < \rho.$$

(21)

Let  $r_i$  be a 2 × 1 zero matrix, and the closed-loop system (20) is modified to the following form:

$$\begin{bmatrix} x_i[k+1] \\ o_i[k] \end{bmatrix} = (\mathbf{A} + \mathbf{BKC}) \begin{bmatrix} x_i[k] \\ d_i[k] \end{bmatrix}$$

(22)

where the matrices A, B, K, and C are, respectively, equal to

$$\mathbf{A} = \begin{bmatrix} A & E \\ C_1 & F \end{bmatrix}, \mathbf{B} = \begin{bmatrix} B \\ 0 \end{bmatrix}, \mathbf{K} = -K, \mathbf{C} = \begin{bmatrix} C_2 & H \end{bmatrix}. \quad (23)$$

Before carrying out the main work, we introduce the following preliminary lemma.

Lemma 1 [24]: For the square matrices X and S, and the matrices  $T = T^T$ , A, P, L with appropriate dimensions, the following two inequalities are equivalent:

$$\begin{bmatrix} T + (LA) + (LA)^T & * \\ XP^T - XL^T + SA & -SX^T - XS^T \end{bmatrix} < 0$$

(24)

$$T + (PA) + (PA)^T < 0.$$

(25)

Proof:

$(24) \Rightarrow (25)$ : From (24), the inequality  $-SX^T - XS^T < 0$  is obtained. This means that X is a nonsingular matrix. Through pre- and post-multiplying (24) with  $[I, A^TX^{-1}]$  and its transpose, we have

$$\begin{bmatrix} I & \mathbf{A}^{T}\mathbf{X}^{-1} \end{bmatrix} \begin{bmatrix} \mathbf{T} + (\mathbf{L}\mathbf{A}) + (\mathbf{L}\mathbf{A})^{T} & * \\ \mathbf{X}\mathbf{P}^{T} - \mathbf{X}\mathbf{L}^{T} + \mathbf{S}\mathbf{A} & -\mathbf{S}\mathbf{X}^{T} - \mathbf{X}\mathbf{S}^{T} \end{bmatrix} \begin{bmatrix} I \\ \mathbf{X}^{-T}\mathbf{A} \end{bmatrix}$$

$$= \begin{bmatrix} (\mathbf{T} + (\mathbf{L}\mathbf{A}) + (\mathbf{L}\mathbf{A})^{T} + \mathbf{A}^{T}\mathbf{X}^{-1}(\mathbf{X}\mathbf{P}^{T} - \mathbf{X}\mathbf{L}^{T} + \mathbf{S}\mathbf{A}))^{T} \\ ((\mathbf{X}\mathbf{P}^{T} - \mathbf{X}\mathbf{L}^{T} + \mathbf{S}\mathbf{A})^{T} + \mathbf{A}^{T}\mathbf{X}^{-1}(-\mathbf{S}\mathbf{X}^{T} - \mathbf{X}\mathbf{S}^{T}))^{T} \end{bmatrix}^{T}$$

$$\times \begin{bmatrix} I \\ \mathbf{X}^{-T}\mathbf{A} \end{bmatrix}$$

$$= \begin{bmatrix} (\mathbf{T} + (\mathbf{L}\mathbf{A}) + (\mathbf{L}\mathbf{A})^{T} + \mathbf{A}^{T}\mathbf{P}^{T} - \mathbf{A}^{T}\mathbf{L}^{T} + \mathbf{A}^{T}\mathbf{X}^{-1}\mathbf{S}\mathbf{A})^{T} \\ ((\mathbf{X}\mathbf{P}^{T} - \mathbf{X}\mathbf{L}^{T} + \mathbf{S}\mathbf{A})^{T} - \mathbf{A}^{T}\mathbf{X}^{-1}\mathbf{S}\mathbf{X}^{T} - \mathbf{A}^{T}\mathbf{S}^{T})^{T} \end{bmatrix}^{T}$$

$$\times \begin{bmatrix} I \\ \mathbf{X}^{-T}\mathbf{A} \end{bmatrix}$$

$$= T + (LA) + (LA)^{T} + A^{T}P^{T} - A^{T}L^{T} + A^{T}X^{-1}SA + ((XP^{T} - XL^{T} + SA)^{T} - A^{T}X^{-1}SX^{T} - A^{T}S^{T})^{T}(X^{-T}A) = T + (PA) + (PA)^{T} < 0.$$

(26)

Hence, (25) is obtained.

$(25) \Rightarrow (24)$ : Let L = P, S = I, and X =  $\varkappa I$ , where the scalar  $\varkappa > 0$ , the matrix inequality (24) is modified to

$$\begin{bmatrix} T + (PA) + (PA)^T & A^T \\ A & -2\varkappa I \end{bmatrix} < 0.$$

(27)

Based on the Schur complement, (27) is rewritten as

$$T + (PA) + (PA)^{T} + \frac{1}{2\varkappa}A^{T}A < 0.$$

(28)

Since  $T + (PA) + (PA)^T < 0$  holds, the sufficient large number  $\varkappa > 0$  guarantees that the above inequality (28) is true.

Theorem 1: Given a spanning-tree clock synchronization network denoted by  $\mathcal{G}$ , consisting of a perfect root node's clock and N sensor node clocks with nonidentical and drifting frequencies  $f_i[k] \in \{f_i[k]: f_i[k] \neq f_0 \text{ and } i \in \mathcal{N}\}$ , and a scalar  $\rho > 0$ . For the known parameters  $\zeta$  and  $\xi \neq 0$ , if there exist the matrices  $Q > 0 \in \mathbb{R}^{2\times 2}$  and  $G \in \mathbb{R}^{3\times 3}$ , and the diagonal matrices  $V \in \mathbb{R}^{2\times 2}$  and  $U \in \mathbb{R}^{2\times 2}$  such that

$$\begin{bmatrix} \Phi_1 & * & * \\ \Psi_1 & \Psi_2 & * \\ \Phi_2 & (\xi G\mathbf{B} - \mathbf{B}U)^T & -(\mathbf{B}^T \mathbf{B}U) - (\mathbf{B}^T \mathbf{B}U)^T \end{bmatrix} < 0$$

(29)

where  $\Phi_1 = -\mathrm{diag}(Q, \rho^2 I) + (\zeta H \mathbf{B} V \mathbf{C}) + (\zeta H \mathbf{B} V \mathbf{C})^T$ ,  $\Phi_2 = (\mathbf{B}^T \mathbf{B} V \mathbf{C}) - (\zeta H \mathbf{B} U)^T$ ,  $\Psi_1 = G \mathbf{A} + \mathbf{B} V \mathbf{C}$ ,  $\Psi_2 = -G - G^T + \mathrm{diag}(Q, I)$ ,  $H = [I \in \mathbb{R}^{3 \times 3}, 0 \in \mathbb{R}^{3 \times 3}]^T$ , and the control gain matrix is  $\mathbf{K} = \xi U^{-1} V$ , then the prescribed  $H_{\infty}$  performance (21) is guaranteed.

*Proof:* The directed spanning-tree system  $\mathcal{G}$  can be decomposed into N 2-D systems (22). For an arbitrary closed-loop pairwise system, suppose that (29) holds,  $-(\mathbf{B}^T\mathbf{B}U) - (\mathbf{B}^T\mathbf{B}U)^T < 0$  implies that U is a nonsingular matrix. By defining  $U = \xi \mathbf{U}$ , and letting the matrices T, L, A, P, S, and X in Lemma 1 equal to

$$T = \begin{bmatrix} -\operatorname{diag}(Q, \rho^{2}I) & \Psi_{1}^{T} \\ \Psi_{1} & \Psi_{2} \end{bmatrix}$$

$$L = \begin{bmatrix} (\zeta H \mathbf{B} \mathbf{U})^{T} & 0 \end{bmatrix}^{T}, \mathbf{A} = \mathbf{U}^{-1} V \begin{bmatrix} \mathbf{C} & 0 \end{bmatrix}$$

$$P = \begin{bmatrix} 0 & (G \mathbf{B} - \mathbf{B} \mathbf{U})^{T} \end{bmatrix}^{T}, \mathbf{S} = \mathbf{B}^{T} \mathbf{B} \mathbf{U}, \mathbf{X} = \xi I.$$

From (25) of Lemma 1, the following matrix inequality is obtained:

$$\begin{bmatrix} -\operatorname{diag}(Q, \rho^{2}I) & \Psi_{1}^{T} \\ \Psi_{1} & \Psi_{2} \end{bmatrix} + \begin{bmatrix} 0 \\ G\mathbf{B} - \mathbf{B}\mathbf{U} \end{bmatrix} \mathbf{U}^{-1}V[\mathbf{C} \quad 0]$$

$$+ \left( \begin{bmatrix} 0 \\ G\mathbf{B} - \mathbf{B}\mathbf{U} \end{bmatrix} \mathbf{U}^{-1}V[\mathbf{C} \quad 0] \right)^{T}$$

$$= \begin{bmatrix} -\operatorname{diag}(Q, \rho^{2}I) & \Psi_{1}^{T} \\ \Psi_{1} & \Psi_{2} \end{bmatrix}$$

$$+ \left( \begin{bmatrix} 0 & I \end{bmatrix}^{T}(G\mathbf{B} - \mathbf{B}\mathbf{U})\mathbf{U}^{-1}V[\mathbf{C} \quad 0] \right)^{T} < 0. \quad (30)$$

$$+ \left( \begin{bmatrix} 0 & I \end{bmatrix}^{T}(G\mathbf{B} - \mathbf{B}\mathbf{U})\mathbf{U}^{-1}V[\mathbf{C} \quad 0] \right)^{T} < 0. \quad (30)$$

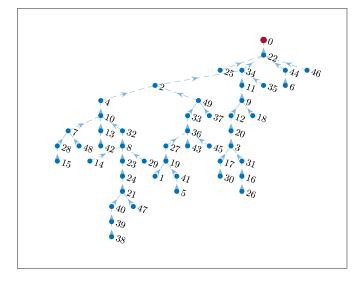

Fig. 3. 50-node spanning-tree clock synchronization network.

Through defining  $\mathbf{K} = \mathbf{U}^{-1}V$ , according to (30), we have

$$\begin{bmatrix} -\operatorname{diag}(Q, \rho^{2}I) & (G\mathbf{A} + \mathbf{B}V\mathbf{C})^{T} \\ G\mathbf{A} + \mathbf{B}V\mathbf{C} & -G - G^{T} + \operatorname{diag}(Q, I) \end{bmatrix} \\ + \left( \begin{bmatrix} 0 & I \end{bmatrix}^{T} (G\mathbf{B} - \mathbf{B}\mathbf{U})\mathbf{U}^{-1}V \begin{bmatrix} \mathbf{C} & 0 \end{bmatrix} \right) \\ + \left( \begin{bmatrix} 0 & I \end{bmatrix}^{T} (G\mathbf{B} - \mathbf{B}\mathbf{U})\mathbf{U}^{-1}V \begin{bmatrix} \mathbf{C} & 0 \end{bmatrix} \right)^{T} \\ = \begin{bmatrix} -\operatorname{diag}(Q, \rho^{2}I) & (G\mathbf{A} + G\mathbf{B}\mathbf{K}\mathbf{C})^{T} \\ G\mathbf{A} + G\mathbf{B}\mathbf{K}\mathbf{C} & -G - G^{T} + \operatorname{diag}(Q, I) \end{bmatrix} < 0. \quad (31)$$

Based on [24] and [25], (31) is the bounded real lemma with the auxiliary variable matrix G. Once the matrix inequality (29) is established, the  $H_{\infty}$  performance  $\rho$  of any arbitrary pairwise system (22) is guaranteed. Since the spanning-tree network is a directed graph, the  $H_{\infty}$  performance of the networked system G is also guaranteed. This means that clock and delay noises in the spanning-tree clock synchronization network possess a small impact (i.e.,  $\rho$  times) on the output accuracy.

#### IV. SIMULATION RESULTS

To validate the theoretical results in the preceding section, here, we conduct numerical simulations in a (randomly generated) 50-node spanning-tree network (see Fig. 3). For the simulations, the initial clock offset  $\theta_i[0]$  and initial skew  $\gamma_i[0]$  are chosen randomly and uniformly in the corresponding intervals (0.4 s, 0.8 s) and (0 ppm, 50 ppm). The clock offset and skew are subject to random perturbations with the standard deviations  $\sigma_{\theta_i} = 1$   $\mu$ s and  $\sigma_{\gamma_i} = 1$  ppm, respectively. The synchronization cycle is 1 s. The standard deviation of packet-exchange delay is  $\sigma_{\kappa_i} = 4$   $\mu$ s [11]. This means that the standard deviations of offset and skew measurement noises [see (15)] are, respectively, 4  $\mu$ s and around 6  $\mu$ s.

The condition in Theorem 1 is used to design a static output feedback controller, the  $H_{\infty}$  performance  $\rho=14.671$  is obtained under  $\zeta=0.4895$  and  $\xi=0.4937$ . The control gain

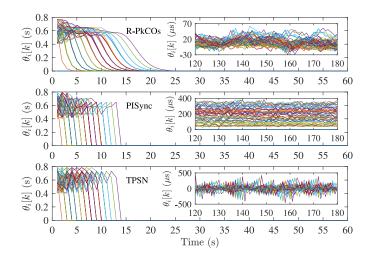

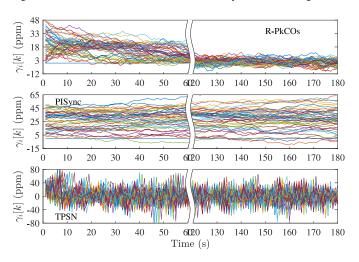

Fig. 4. Evolution of the clock offset under three synchronization algorithms.

Fig. 5. Evolution of the clock skew via R-PkCOs, PISync, and TPSN.

K is equal to

$$K = \begin{bmatrix} 0.7615 & 0\\ 0 & 0.1253 \end{bmatrix}$$

In addition, two synchronization approaches, namely, PISync and TPSN, are also selected for performance comparison. Figs. 4 and 5, respectively, show the evolution of offset and skew over time. Clearly, all three solutions let both the clock offset and skew converge to corresponding constant values, and thus the steady synchronized state is achieved in the network. In the PISync and TPSN protocols, since the complete offset estimate is used for clock correction (i.e.,  $\alpha = 1$ ), their convergence speed is faster than that of R-PkCOs (see Fig. 4).

Even though the adaptive tuning method is utilized in PISync, the order of magnitude of  $\beta$  is still tiny and is less than  $5 \times 10^{-07}$  (from the simulation results). Thus, such a small value of  $\beta$  cannot overcome the joint effects from the drifting clock frequency (with the standard deviation of 1 ppm) and  $\nu_{\gamma_i}[k]$  (with the standard deviation of 6  $\mu$ s). The failure of clock kew correction (see Fig. 5) also leads to worse precision of around 400  $\mu$ s, as shown in Fig. 4. For the TPSN protocol, the drifting clock is adjusted by using the full clocks kew estimate (i.e.,  $\beta = 1$ ), which suffers from large clocks kew

Fig. 6. Evolution of  $\aleph_i = [(\|z_i\|_2)/(\|d_i\|_2)]$  under three clock synchronization methods.

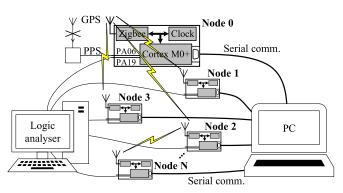

Fig. 7. Architecture of the wireless network hardware tested.

measurement noise  $v_{\gamma_i}[k]$  with the standard deviation of 6  $\mu$ s (while the frequency's standard deviation is only about 1 ppm). As a result, an overcorrection occurs on  $\gamma_i[k]$  (see Fig. 5), and the synchronization performance degrades. In R-PkCOs, the control gain K is obtained from Theorem 1, which implies that a small (i.e., less than  $\rho = 14.671$  times) effect of clock and delay disturbances is on the output synchronization accuracy. Thus, the R-PkCOs protocol achieves better precision, compared to PISync and TPSN.

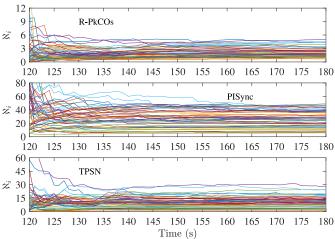

For PISync and TPSN, their corresponding under- and over-correction are also reflected in the evolution of  $\aleph_i = [(\|z_i\|_2)/(\|d_i\|_2)]$  (see Fig. 6). The proposed R-PkCOs method guarantees  $\aleph_i$  of each node is smaller than 6. However, during the steady synchronized state,  $\aleph_i$  of PISync and TPSN are only about 50 and 30, respectively.

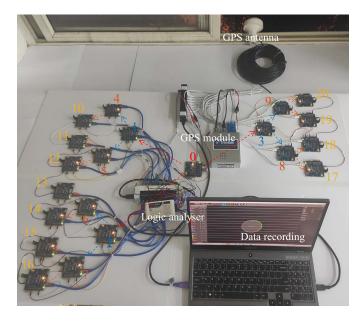

## V. EXPERIMENTAL EVALUATION

This section evaluates the performance of the proposed R-PkCOs synchronization method in a spanning-tree network (see Figs. 7 and 8). For the implementation, the clock's time variable is represented by a 32-bit counter register (i.e., COUNT) of the RTC module, which is driven by an external 32.768 MHz crystal oscillator. The threshold register (i.e., COMP) is set to 32767999 to let the embedded clock reset each second. Once COUNT matches COMP, the processor issues a hardware interrupt, where COUNT is reset to zero,

Fig. 8. Hardware tested (dashed line: Sync packet exchange direction).

# Algorithm 1 R-PkCOs Synchronisation Protocol

```

1: Initialisation

configure parameters; k = 0;

2:

3:

initialise RF;

initialise RTC:

4:

5: IRQ: Clock Firing

reset counter (counter = 0);

6:

send pkt(Sync);

7:

8: AMI: Reception of A Sync Packet

read counter (\tilde{P}_i[k] = \text{counter});

9:

estimate clock offset, according to (13);

10:

11:

adjust clock threshold, based on (14):

threshold = threshold + u_{\varphi_i}[k];

12:

correct counter, following:

13:

if (P_i[k] + u_{\theta_i}[k] + \bar{\eta}_i) < \text{threshold then}

14:

counter = \hat{P}_i[k] + u_{\theta_i}[k] + \bar{\eta}_i;

15:

16:

elseif (P_i[k] + u_{\theta_i}[k] + \bar{\eta}_i) \ge threshold then

reset counter (counter = 0);

17:

18:

send_pkt(Sync);

end if

19.

k = k + 1;

20:

```

meanwhile, a 21-byte *Sync* packet is transmitted. Upon the reception of the wireless packet, the other hardware interrupt [i.e., address match interrupt (AMI)] is triggered to generate a timestamp, which is used for offset calculation and clock correction. In addition, Algorithm 1 presents the pseudocode of R-PkCOs.

During the experiments, the Trimble ThunderBolt E GPS Disciplined Clock [26] is connected to the root node, for providing the reference time [i.e., the pulse-per-second (PPS) signal] to the network (see Figs. 7 and 8). This means that the synchronization cycle T is one second. The average values of packet-exchange and processing delays are around 514.25 and 117  $\mu$ s, respectively, and the corresponding standard

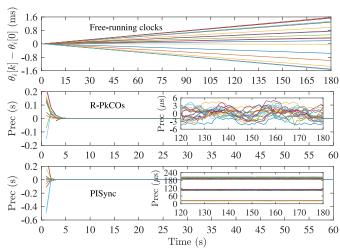

Fig. 9. Evolution of free-running embedded clocks, and the synchronization precision by using the R-PkCOs and PISync protocols.

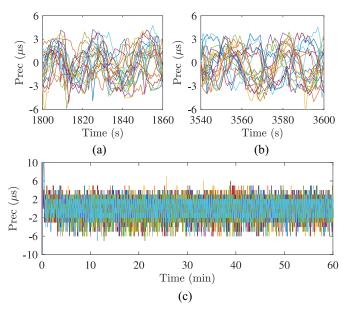

Fig. 10. One-hour performance of the R-PkCOs scheme via (a), (b) the logic analyzer, and (c) serial communication methods.

deviations are of 0.3 and 0.3  $\mu$ s. The control gains  $\alpha$  and  $\beta$  are 1/1.3 and 1/8, respectively, which are the same as the parameters used in the simulations.  $t_{dp}$  and  $t_{sd}$  are set to 9.15 and 3.66 ms, respectively. The logic analyzer [27] is used to evaluate the performance, and the synchronization precision is defined as the time difference between the sensor node clock and root node's clock. Moreover, the PISync protocol is chosen for comparison.

From Fig. 9, it can be seen that each sensor node possess a unique frequency drifting characteristic. The clock offset increments of 20 sensor nodes in the experiments are between -1.6 and 1.6 ms, if no time synchronization protocol is applied to the network. By using the proposed R-PkCOs protocol, the synchronization precision in the spanning-tree network is up to 6  $\mu$ s; while, the first-hop node precision of PISync is about  $20 \mu$ s, which also coincides with [21].

In addition, we also study the one-hour performance of the R-PkCOs protocol. The logic analyzer can only sample 100-s

data; thus, the serial communication method [11] is utilized for data collection and analysis. Fig. 10(c) shows the time synchronization precision obtained by using the serial communication method. The precision converges from the initial value to around 6  $\mu$ s, and this accuracy [from Fig. 10(c)] is similar to the performance calculated via the logic analyzer, as shown in Fig. 10(a) and (b). Overall, by using the slot-based one-way Sync packet transmission scheme and the control gain obtained from Theorem 1, R-PkCOs achieves time synchronization with the precision of about 6  $\mu$ s during the one-hour experiments.

#### VI. CONCLUSION

In this article, we proposed the R-PkCOs protocol to correct both clock skew and offset for improving synchronization performance, subject to the impacts of drifting frequency, and external perturbations from packet-exchange and processing delays. The proposed algorithm not only uses the slot-based one-way Sync packet transmission mechanism but also adopts the  $H_{\infty}$  control method to guide the parameter selection, for letting clock and delay noises possess a tiny (i.e.,  $\rho$  times) impact on the synchronization accuracy. Through designing the static controller, the ratio between the modulus of the achieved synchronization precision and the magnitude of clock and delay noises is always smaller than a given value  $\rho$ , thereby guaranteeing robustness of R-PkCOs. The one-hour experimental results show that the proposed protocol is capable of achieving clock synchronization with the precision of 6 ms in a 21-node spanning-tree network. Thus, the R-PkCOs synchronization technology can be applied in the IIoT applications to provide an accurate common sense of timing (up to 6  $\mu$ s) among wireless nodes.

## ACKNOWLEDGMENT

The authors would like to thank Mr. Jun Xiong and Prof. Xiao-Heng Chang for providing help in the development of the linear matrix inequality (LMI) program on MATLAB.

#### REFERENCES

- [1] A. M. Romanov, F. Gringoli, and A. Sikora, "A precise synchronization method for future wireless TSN networks," *IEEE Trans. Ind. Informat.*, vol. 17, no. 5, pp. 3682–3692, May 2021.

- [2] E. Sisinni, A. Saifullah, S. Han, U. Jennehag, and M. Gidlund, "Industrial Internet of Things: Challenges, opportunities, and directions," *IEEE Trans. Ind. Informat.*, vol. 14, no. 11, pp. 4724–4734, Nov. 2018.

- [3] T. Qiu, Y. Zhang, D. Qiao, X. Zhang, M. L. Wymore, and A. K. Sangaiah, "A robust time synchronization scheme for Industrial Internet of Things," *IEEE Trans. Ind. Informat.*, vol. 14, no. 8, pp. 3570–3580, Aug. 2018.

- [4] Z. Hanzalek and P. Jurčik, "Energy efficient scheduling for cluster-tree wireless sensor networks with time-bounded data flows: Application to IEEE 802.15.4/ZigBee," *IEEE Trans. Ind. Informat.*, vol. 6, no. 3, pp. 438–450, Aug. 2010.

- [5] T. Qiu, X. Liu, M. Han, H. Ning, and D. O. Wu, "A secure time synchronization protocol against fake timestamps for large-scale Internet of Things," *IEEE Internet Things J.*, vol. 4, no. 6, pp. 1879–1889, Dec. 2017.

- [6] H. M. Smith, "Synchronous flashing of fireflies," *Science*, vol. 82, no. 2120, pp. 151–152, Aug. 1935.

- [7] R. E. Mirollo and S. H. Strogatz, "Synchronization of pulse-coupled biological oscillators," SIAM J. Appl. Math., vol. 50, no. 6, pp. 1645–1662, 1990.

- [8] Y. Zong, X. Dai, P. Canyelles-Pericas, K. Busawon, R. Binns, and Z. Gao, "Modelling and synchronisation of delayed packet-coupled oscillators in industrial wireless sensor networks," in *Proc. 21st IFAC World Congr. (IFAC)*, Jul. 2020, pp. 8381–8387.

- [9] IEEE Standard for Low-Rate Wireless Networks, IEEE Standard 802.15.4–2020, 2020.

- [10] Y. Zong, X. Dai, Z. Gao, K. Busawon, R. Binns, and I. Elliott, "Synchronization of pulse-coupled oscillators for IEEE 802.15.4 multihop wireless sensor networks," in *Proc. Conf. Commun. (GlobeCom)*, Dec. 2018, pp. 1–7.

- [11] Y. Zong, X. Dai, and Z. Gao, "Proportional-integral synchronization for nonidentical wireless packet-coupled oscillators with delays," *IEEE Trans. Ind. Electron.*, vol. 68, no. 11, pp. 11598–11608, Nov. 2021.

- [12] J. Elson, L. Girod, and D. Estrin, "Fine-grained network time synchronization using reference broadcasts," in *Proc. 5th Symp. Oper. Syst. Design Implement.*, 2002, pp. 147–163.

- [13] S. Ganeriwal, R. Kumar, and M. B. Srivastava, "Timing-sync protocol for sensor networks," in *Proc. 1st Int. Conf. Embedded Netw. Sensor Syst. (SenSys)*, Nov. 2003, pp. 138–149.

- [14] F. Shi, X. Tuo, S. X. Yang, J. Lu, and H. Li, "Rapid-flooding time synchronization for large-scale wireless sensor networks," *IEEE Trans. Ind. Informat.*, vol. 16, no. 3, pp. 1581–1590, Mar. 2020.

- [15] K. S. Yildirim, R. Carli, and L. Schenato, "Adaptive proportional-integral clock synchronization in wireless sensor networks," *IEEE Trans. Control* Syst. Technol., vol. 26, no. 2, pp. 610–623, Mar. 2018.

- [16] G. J. Pottie and W. J. Kaiser, "Wireless integrated network sensors," Commun. ACM, vol. 43, pp. 51–58, May 2000.

- [17] F. Lin, W. Dai, W. Li, Z. Xu, and L. Yuan, "A framework of priority-aware packet transmission scheduling in cluster-based industrial wireless sensor networks," *IEEE Trans. Ind. Informat.*, vol. 16, no. 8, pp. 5596–5606, Aug. 2020.

- [18] H. Wang, L. Shao, M. Li, B. Wang, and P. Wang, "Estimation of clock skew for time synchronization based on two-way message exchange mechanism in industrial wireless sensor networks," *IEEE Trans. Ind. Informat.*, vol. 14, no. 11, pp. 4755–4765, Nov. 2018.

- [19] X. Huan, K. Kim, S. Lee, E. Lim, and A. Marshall, "A beaconless asymmetric energy-efficient time synchronization scheme for resourceconstrained multi-hop wireless sensor networks," *IEEE Trans. Commun.*, vol. 68, no. 3, pp. 1716–1730, Mar. 2020.

- [20] Z. An, H. Zhu, X. Li, C. Xu, Y. Xu, and X. Li, "Nonidentical linear pulse-coupled oscillators model with application to time synchronization in wireless sensor networks," *IEEE Trans. Ind. Electron.*, vol. 58, no. 6, pp. 2205–2215, Jun. 2011.

- [21] Y.-P. Tian, S. Chun, G. Chen, S. Zong, Y. Huang, and B. Wang, "Delay compensation-based time synchronization under random delays: Algorithm and experiment," *IEEE Trans. Control Syst. Technol.*, vol. 29, no. 1, pp. 80–95, Jan. 2021.

- [22] Y. Zong, X. Dai, Z. Gao, K. Busawon, and J. Zhu, "Modelling and synchronization of pulse-coupled non-identical oscillators for wireless sensor networks," in *Proc. 16th Int. Conf. Ind. Informat. (INDIN)*, Jul. 2018, pp. 101–107.

- [23] G. Giorgi and C. Narduzzi, "Performance analysis of Kalman-filter-based clock synchronization in IEEE 1588 networks," *IEEE Trans. Instrum. Meas.*, vol. 60, no. 8, pp. 2902–2909, Aug. 2011.

- [24] X.-H. Chang, R.-R. Liu, and J. H. Park, "A further study on output feedback  $H_{\infty}$  control for discrete-time systems," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 67, no. 2, pp. 305–309, Feb. 2020.

- [25] S. Boyd, L. E. Ghaoui, E. Feron, and V. Balakrishnan, *Linear Matrix Inequalities in System and Control Theory*. Philadelphia, PA, USA: SIAM, 1994.

- [26] "The trimble thunderbolt E GPS disciplined clock." [Online]. Available: https://timing.trimble.com/products/disciplined-clocks/thunderbolt-e-gps-disciplined-clock/ (accessed Feb. 13, 2022).

- [27] "Kingst logic analyser", 2016. [Online]. Available: http://www.qdkingst.com/en/products (accessed Feb. 13, 2022).

Yan Zong (Member, IEEE) received the B.Eng. degree in electrical and electronic engineering from Nanjing Normal University, Nanjing, China, in 2016, and the Ph.D. degree in electrical engineering from Northumbria University, Newcastle upon Tyne, U.K., in 2020.

He is currently a Research Fellow with Cranfield University, Cranfield, U.K. Prior to that he was a FPGA Engineer with Keiky Ltd., Earley, U.K. His research interests cut across several disciplines, which include machine learning, networked control

systems and synchronization, and their applications to the Industrial Internet of Things.

**Xuewu Dai** (Member, IEEE) received the B.Eng. degree in electronic engineering and the M.Sc. degree in computer science from Southwest University, Chongqing, China, in 1999 and 2003, respectively, and the Ph.D. degree from the University of Manchester, Manchester, U.K., in 2008

He is a Senior Lecturer with the Department of Mathematics, Physics and Electrical Engineering, Northumbria University, Newcastle upon Tyne, U.K. Prior to that he was a Postdoctoral Researcher with

the Department of Engineering Science, University of Oxford, Oxford, U.K., from 2011 to 2013, and with the Department of Electronic and Electrical Engineering, University of College, London, U.K., from 2009 to 2011. His research interests include robust state estimation, networked control systems and synchronization, and their applications to the time-sensitive Industrial Internet of Things.

Dr. Dai was awarded the Early Career Research Prize by SWIG U.K.

**Zhuangkun Wei** received the bachelor's and master's degrees in electronic engineering from Beijing University of Posts and Telecommunications, Beijing, China, in 2014 and 2018, respectively, and the Ph.D. degree in engineering from the University of Warwick, Coventry, U.K., in 2021.

He is currently a Research Fellow with the School of Aerospace, Transport and Manufacturing, Cranfield University Cranfield, U.K. His research interests cover physical-layer security, graph signal processing, molecular communications, and

explainable artificial intelligence.

Mengbang Zou received the M.Sc. degree in mechanical science and engineering from Huazhong University of Science and Technology, Wuhan, China, in 2019. He is currently pursuing the Ph.D. degree with the School of Aerospace, Transport and Manufacturing, Cranfield University, Cranfield, U.K.

He is interested in complex system with nonlinear dynamics, including complex system's resilience, synchronization, and region of attraction.

**Weisi Guo** (Senior Member, IEEE) received the Ph.D. degree from the University of Cambridge, Cambridge, U.K., in 2011.

He is currently a Full Professor and the Head of Human–Machine Intelligence Group, Cranfield University, Cranfield, U.K. He was an Assistant Professor with the University of Warwick, Coventry, U.K., from 2012 to 2019, and a Turing Fellow from 2017 to 2019. His research interests focus on networks, data science, and autonomy.

Prof. Guo was a winner of the IET Innovation Award.

**Zhiwei Gao** (Senior Member, IEEE) received the B.Eng. degree in electrical engineering and automation and the M.Eng. and Ph.D. degrees in systems engineering from Tianjin University, Tianjin, China, in 1987, 1993, and 1996, respectively.

He is currently with the Faculty of Engineering and Environment, Northumbria University, Newcastle upon Tyne, U.K., as a Reader. His research interests include stochastic control systems, data-driven modeling, estimation and filtering, fault diagnosis, resilient control, intelligent

optimization, power electronics, wind energy systems, electric vehicle batteries, and bioinformatics.

Dr. Gao serves several leading international journals as academic editors, and organized more than 10 special issues in the premier international journals.